【導讀】在高速電路設計中,鏈路中的每一個參數(shù)都有可能導致傳遞的信號出問題。今天就和大家分享一個平常大家不太注意的參數(shù)。

先回顧下在中學的時候,咱們學習的一個概念,趨膚效應:當信號的頻率較越來越高時,信號都會趨向于導體的表面?zhèn)鬟f。這樣就會導致信號流過導體的相對有效面積變小,從電阻的角度來分析,這就會導致電阻增加,導致傳遞能量的損失。

在電子產(chǎn)品使用的PCB,基本都是由銅箔和有機材料組成的,如下圖所示:

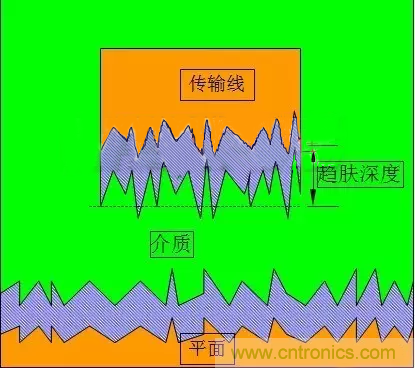

我們平時看到的銅箔,表面上看起來都是非常光滑的,實際上并不如你肉眼所見的那樣,銅箔并不是完全光滑的,其在進項顯微鏡下如下圖所示:

為了更加的容易理解,給大家做一個示意圖,如下圖所示:

銅箔的表面都是有很多銅牙存在的。目前小編沒有發(fā)現(xiàn)非常官方的數(shù)據(jù)說明普通的銅牙到底有多長,據(jù)小編看到的普通的銅箔,沒有經(jīng)過處理的銅牙(銅箔粗糙度)一般都是在20~30um左右。當然,常規(guī)的根據(jù)銅箔粗糙度的厚度(系數(shù))不同,目前有標準銅箔、反轉銅箔、低粗糙度銅箔和超低粗糙度銅箔之分。

前面說到,銅箔的粗糙度會影響到信號完整性,那么我們就來做一個實驗看看。原理圖如下所示,把銅箔粗糙度的設置為一個變量,初始值為0,仿真的速率為10Gbps:

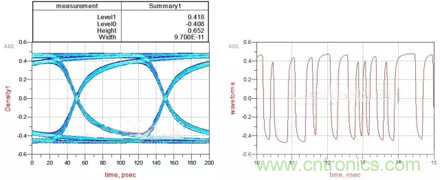

分別查看其眼圖和波形,如下所示:

從結果可以看到:眼圖的寬度為97ps,高度為0.652V,信號的峰值為0.479V。

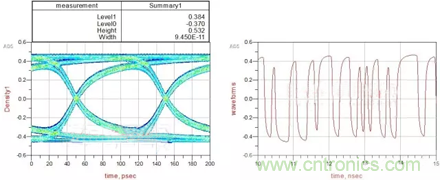

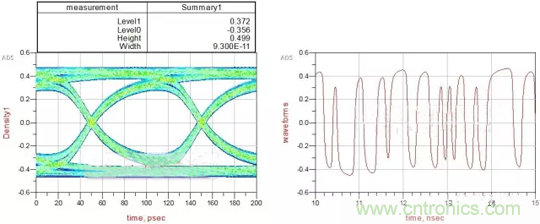

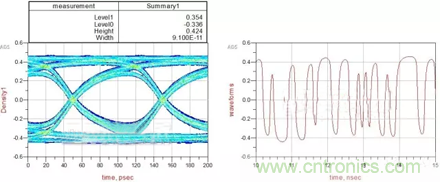

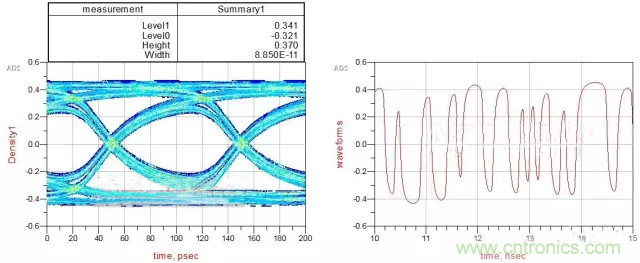

那么,接下來,逐步改變銅箔粗糙度的厚度,觀察眼圖的變化,分別仿真銅箔粗糙度為5um、10um、15um和20um的情況,眼圖和波形分別如下所示:

當粗糙度為5um的時候,眼圖的寬度為94.5ps,高度為0.532V。

當粗糙度為10um的時候,眼圖的寬度為93ps,高度為0.499V。

當粗糙度為15um的時候,眼圖的寬度為91ps,高度為0.424V。

當粗糙度為20um的時候,眼圖的寬度為88.5ps,高度為0.370V。

從以上的結果,咱們可以看到當銅箔粗糙度的系數(shù)(厚度)增加時,眼圖的的margin越來越小,抖動(Jitter)越來越大。

有的工程師經(jīng)常會問到這樣一個問題:當信號的速率為多少的時候,在實際項目工程中需要考慮銅箔粗糙度的影響。我的答案是,任何時候考慮都是必要的。但是綜合成本和效果來考慮的話,當信號速率超過5G以上的時候,就應當適當?shù)目紤]銅箔的選擇問題(如果設計要求不高,也可以不考慮)。

所以,當信號的速率越來越高的時候,我們不僅僅需要關注芯片的驅動能力、PCB介質的介電常數(shù)、介質損耗角、連接器、線纜等等,還需要考慮到導體(銅)的表面粗糙度的影響。