【導(dǎo)讀】隨著數(shù)字通信技術(shù)的發(fā)展,由于FPGA的靈活性與其較短的開(kāi)發(fā)周期,在接口電路設(shè)計(jì)中的應(yīng)用已經(jīng)越來(lái)越廣泛。本文提出一種使用FPGA實(shí)現(xiàn)PIC—I2S 的接口轉(zhuǎn)換電路,不僅可以避免使用協(xié)議轉(zhuǎn)換芯片,節(jié)省電路板上的空間,而且還大幅加強(qiáng)了系統(tǒng)的靈活性,方便維護(hù)升級(jí)。

I2S總線是一種用于音頻設(shè)備間傳輸數(shù)據(jù)的串行總線標(biāo)準(zhǔn),該總線采用獨(dú)立的時(shí)鐘線與數(shù)據(jù)線,避免了時(shí)差誘發(fā)的失真。隨著多媒體的廣泛應(yīng)用,該總線已被應(yīng)用于越來(lái)越多的數(shù)字系統(tǒng)中。

PCI總線是一種高性能的32/64位局部總線,理論最大傳輸速率可達(dá)132 Mbit/s,可支持多組外設(shè),已經(jīng)被各類主流處理器做為總線標(biāo)注,是目前應(yīng)用最廣泛的外圍總線。如今大部分處理器并沒(méi)有集成I2S接口,但在嵌入式系統(tǒng)中CPU經(jīng)常使用PCI總線與外圍設(shè)備進(jìn)行交互,故需設(shè)計(jì)一種PCI—I2S接口轉(zhuǎn)換電路,從而實(shí)現(xiàn)CPU與外圍音頻設(shè)備進(jìn)行通信。目前實(shí)現(xiàn)此種接口轉(zhuǎn)換電路主要通過(guò)PCI接口芯片與音頻接口芯片等專用集成電路芯片在板級(jí)電路進(jìn)行組合從而實(shí)現(xiàn)基于PCI的音頻播放設(shè)備。此種電路雖然成熟可靠,但電路設(shè)計(jì)復(fù)雜、靈活性小而且需要占用大量的電路板空間。

1 系統(tǒng)的硬件設(shè)計(jì)

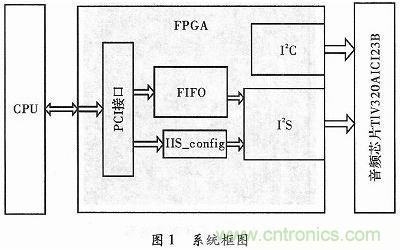

音頻播放系統(tǒng)主要由立體聲音頻編解碼器TLN320AIC23B,F(xiàn)PGA器件XC6SLX75以及處理器PowerPC8270組成。系統(tǒng)框圖如圖1所示,CPU將原始音頻數(shù)據(jù)通過(guò)PCI總線傳至FPGA后以每組數(shù)據(jù)16 bit的格式串行傳輸至音頻芯片TLV320AIC23B,并由音頻芯片將數(shù)字量轉(zhuǎn)換為模擬音頻信號(hào)輸出。FPGA實(shí)現(xiàn)PCI接口功能和對(duì)音頻編解碼芯片的配置與數(shù)據(jù)傳輸功能,其內(nèi)部主要由PCI協(xié)議接口,I2S協(xié)議接口,I2S配置寄存器,I2C協(xié)議接口以及FIFO存儲(chǔ)器等組成。

TLV320AIC23B在系統(tǒng)中實(shí)現(xiàn)數(shù)字音頻信息到音頻模擬量的轉(zhuǎn)換,在系統(tǒng)上電工作時(shí),首先需要通過(guò)I2C接口配置它的多個(gè)控制寄存器,此后芯片將根據(jù)位傳輸時(shí)鐘(Bclk)與左右聲道控制時(shí)鐘(LRCIN),按控制寄存器中配置的方式采集由FPGA發(fā)送來(lái)的音頻數(shù)據(jù)。接收到的數(shù)據(jù)將傳至芯片內(nèi)部進(jìn)行數(shù)模轉(zhuǎn)換、濾波等處理。

FPGA根據(jù)I2S協(xié)議規(guī)范與芯片要求,由主時(shí)鐘(MCLK)分頻產(chǎn)生位傳輸時(shí)鐘(Bclk)與左右聲道控制時(shí)鐘(LRCIN),與音頻數(shù)據(jù)同步發(fā)送至 TLV320AIC23B。其中左右聲道控制時(shí)鐘(LRCIN)應(yīng)與音頻數(shù)據(jù)的原始采樣級(jí)別頻率相同,根據(jù)I2S的協(xié)議規(guī)范及芯片資料,其位傳輸時(shí)鐘 (Bclk)與芯片的主時(shí)鐘(MCLK)如下:

BCLK=Sampling Size×Sampling Rate (1)

MCLK=Sampling Size×Sampling Rate×384 (2)

式中,Sampling Rate為原始采樣級(jí)別頻率;SamplingSize為采樣大小。

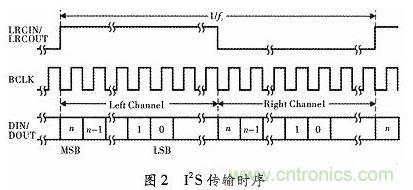

系統(tǒng)中,TLV320AIC23B芯片采用左對(duì)齊的接口模式,其時(shí)序如圖2所示,其中LRCIN為高電平時(shí)音頻的左聲道選通,為低時(shí)音頻的右聲道選通。在 LRCIN的一個(gè)周期內(nèi),左右聲道上傳輸同一組數(shù)據(jù)。由于PCI總線的傳輸速度遠(yuǎn)高于I2S總線的傳輸速度,為不使CPU過(guò)高頻率的響應(yīng)中斷,所以在 FPGA中生成一個(gè)FIFO,可使得PCI總線可以連續(xù)傳入大量數(shù)據(jù)。此外,由于不同的音頻文件有著不同的采樣級(jí)別頻率,而通常音頻文件的采樣頻率為16 kHz或32 kHz,故在FPGA中生成I2S_config寄存器,可以通過(guò)PCI總線設(shè)置此寄存器以調(diào)用FPGA中不同的數(shù)字時(shí)鐘管理(DCM),從而為 TLV320AIC23B芯片提供不同的時(shí)鐘。

2 PCI接口設(shè)計(jì)

PCI協(xié)議比較復(fù)雜,它不僅有嚴(yán)格的同步時(shí)序要求,而且需要許多的配置寄存器,因此實(shí)現(xiàn)電路也比較復(fù)雜。通常情況下,在FPGA中實(shí)現(xiàn)PCI接口通常有3 種方式:(1)用FPGA自行設(shè)計(jì)PCI接口,該方法可根據(jù)需要有選擇地實(shí)現(xiàn)PCI接口功能,更貼近系統(tǒng)需要,而且可以降低系統(tǒng)成本,但需要開(kāi)發(fā)者對(duì) PCI協(xié)議有著深刻的了解,且在外部環(huán)境惡劣時(shí),不容易滿足系統(tǒng)的穩(wěn)定性要求,開(kāi)發(fā)難度較大。(2)利用PCI硬核來(lái)對(duì)系統(tǒng)進(jìn)行開(kāi)發(fā),PCI硬核即是嵌入在FPCA內(nèi)部的固化電路,類似于專用的PCI接口芯片,設(shè)計(jì)者只需完成信號(hào)鏈接與驗(yàn)證即可,但此方法中,PCI硬核已經(jīng)固化在FPGA中,影響了系統(tǒng)的靈活性。(3)利用PCI軟核進(jìn)行開(kāi)發(fā),PCI軟核可以根據(jù)用戶自身的需要進(jìn)行配置,更為靈活,貼近用戶系統(tǒng),且其已經(jīng)過(guò)設(shè)計(jì)廠商的驗(yàn)證,可靠性高。本文采用Mentor公司提供的開(kāi)源軟核MPCI32用于FPGA上PCI接口的開(kāi)發(fā)。

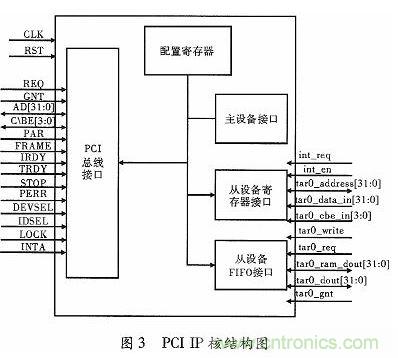

Mentor公司的PCI核完全符合PCI2.2的標(biāo)準(zhǔn),支持33/66 MHz、32位數(shù)據(jù)的傳輸,PCI核的結(jié)構(gòu)如圖3所示,該P(yáng)CI核的功能是將入口測(cè)復(fù)雜的PCI接口信號(hào)轉(zhuǎn)為出口側(cè)較為操作的用戶信號(hào)。PCI核內(nèi)用戶側(cè)設(shè)置有主控制接口和從控制接口以及配置寄存器等模塊,其中從控制接口分為寄存器接口與FIFO接口。因?yàn)楸疚闹袃H使用了從控制接口,所以圖中僅對(duì)從控制接口的信號(hào)展示。可以看出,IP核左側(cè)的信號(hào)為PCI的標(biāo)準(zhǔn)信號(hào),在使用時(shí)與前端PCI總線連接,右側(cè)信號(hào)為本地?cái)?shù)據(jù)信號(hào),可以看出IP核將PCI上原本復(fù)用的地址線與數(shù)據(jù)線處理后分別接出為32位的地址線與32位數(shù)據(jù)線,并且原本總線上雙向的數(shù)據(jù)線被區(qū)分為單向讀信號(hào)線與寫(xiě)信號(hào)線。此外還有后端邏輯對(duì)寄存器的讀寫(xiě)地址信號(hào)線與PCI訪問(wèn)邏輯的讀寫(xiě)地址信號(hào)線,后端對(duì)寄存器使用時(shí)的請(qǐng)求信號(hào)線,寄存器被占用的標(biāo)志信號(hào)線等。配置寄存器包含所有PCI配置空間的信息,其中包括表明設(shè)備信息的Device ID與Ven dor ID寄存器,以及命令寄存器,Base Address Register等主設(shè)備初始化時(shí)需要訪問(wèn)的信息,這些信息在PCI核生成時(shí)已經(jīng)被設(shè)定,無(wú)需改動(dòng)。

在設(shè)計(jì)PCI接口時(shí),用戶通過(guò)發(fā)起寄存器讀寫(xiě)請(qǐng)求tarO_req,去訪問(wèn)后端寄存器,從寄存器交換數(shù)據(jù),在CPU檢測(cè)到都算邏輯未使用寄存器時(shí),可發(fā)起占用請(qǐng)求并占用寄存器(tarO_gnt被置位),此時(shí),PCI讀寫(xiě)此寄存器中的數(shù)據(jù)。

3 音頻接口設(shè)計(jì)

在驅(qū)動(dòng)后端的音頻芯片時(shí)首先需要通過(guò)I2C接口配置音頻芯片的控制寄存器,此后根據(jù)音頻數(shù)據(jù)不同的采樣級(jí)別頻率控制FPGA產(chǎn)生的時(shí)鐘,最終音頻數(shù)據(jù)從FPGA內(nèi)部的FIFO中通過(guò)FPGA產(chǎn)生的時(shí)鐘依據(jù)I2S協(xié)議標(biāo)準(zhǔn)向音頻芯片傳輸。在FPGA中設(shè)計(jì)的音頻接口包括I2C時(shí)序協(xié)議接口模塊,I2S時(shí)鐘控制接口模塊和I2S時(shí)序協(xié)議接口模塊。

3.1 I2C接口模塊的設(shè)計(jì)

I2C總線是由飛利浦公司開(kāi)發(fā)的串行總線,總線由兩根信號(hào)線構(gòu)成,其中SCLK為時(shí)鐘信號(hào)線,SDA為雙向數(shù)據(jù)線。I2C總線上的所有設(shè)備均可做為主設(shè)備,每個(gè)設(shè)備在總線上都有唯一的地址。

立體聲音頻編解碼器TLV320AIC23B中,共有11個(gè)寄存器需要配置,所有寄存器為只寫(xiě)寄存器。這些寄存器分別控制芯片輸出音頻的左右耳機(jī)音量、左右功放音量、芯片電源、采樣率等參數(shù)。在芯片的配置參數(shù)傳輸時(shí),以I2C的數(shù)據(jù)線(SDA)在時(shí)鐘線(SCLK)為高時(shí)下降沿條件作為數(shù)據(jù)的起始位,此后每當(dāng)FPGA向TLV320AIC23B傳輸8位數(shù)據(jù)時(shí),TLV320 AIC23B在第9個(gè)時(shí)鐘時(shí)通過(guò)SDA向FPGA返回一個(gè)ACK信號(hào)。如果FPGA確認(rèn)收到ACK信號(hào)則繼續(xù)傳輸下一組數(shù)據(jù),否則將重復(fù)傳輸此組數(shù)據(jù)。實(shí)際中示波器測(cè)量的傳輸波形如圖4所示。

3.2 I2S時(shí)鐘控制接口模塊的設(shè)計(jì)

由于不同的音頻數(shù)據(jù)有著不同的采樣級(jí)別頻率,所以在傳輸不同音頻文件時(shí),F(xiàn)PGA提供給TLV320AIC23B的時(shí)鐘頻率不同,為使不同采樣頻率的聲音文件都能在本系統(tǒng)上正常播放,故在FPGA內(nèi)部使用其DCM由主時(shí)鐘12.288 MHz生成16 kHz和32 kHz兩種采樣時(shí)鐘頻率,接入緩沖器BUFGMUX中,并且通過(guò)在PCI的配置空間中開(kāi)辟一個(gè)寄存器,寄存器的值接至BUFGMUX的選擇端,這樣通過(guò)配置PCI總線配置此寄存器即可根據(jù)播放音頻的情況選擇時(shí)鐘頻率。

3.3 I2S時(shí)序協(xié)議接口模塊的設(shè)計(jì)

I2S時(shí)序接口模塊的主時(shí)鐘由FPGA內(nèi)部提供,模塊內(nèi)通過(guò)對(duì)主時(shí)鐘進(jìn)行分頻產(chǎn)生BCLK與LRCin,模塊在每個(gè)LRCin的上升沿由緩存FIFO中讀取一個(gè)16 bit的數(shù)據(jù)放入臨時(shí)寄存器,此后在BCLK的每個(gè)上升沿依次由高至低讀取寄存器中的每一位并賦值給數(shù)據(jù)線SDIN,并且在LRCIN的下降延時(shí)重復(fù)傳輸此數(shù)據(jù),從而完成音頻數(shù)據(jù)的I2S協(xié)議傳輸。

4 系統(tǒng)測(cè)試及結(jié)果

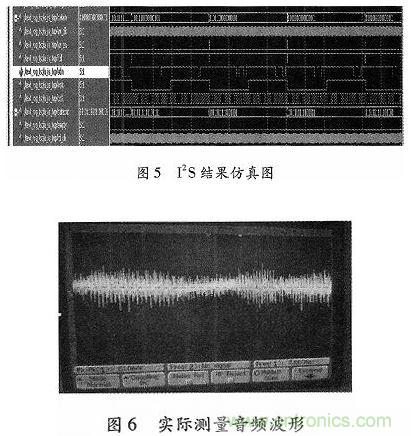

通過(guò)在上位機(jī)中向CPU內(nèi)部Flash燒錄一段音頻數(shù)據(jù),此后通過(guò)訪問(wèn)FPGA的配置寄存器將此段數(shù)據(jù)傳入至FPGA內(nèi)64 kB的FIFO中,后端音頻模塊檢測(cè)到FIFO非空即開(kāi)始工作。首選通過(guò)邏輯仿真軟件對(duì)系統(tǒng)進(jìn)行仿真,結(jié)果如圖5所示,信號(hào)線SDIN、 LRclk,BCLK輸出結(jié)果符合I2S協(xié)議規(guī)范中左對(duì)齊模式。此后可以在音頻芯片模擬輸出端接入耳機(jī)或功放等音頻播放設(shè)備,用示波器測(cè)量其模擬輸出。結(jié)果證明此系統(tǒng)工作正常,可以按照要求播放16 kbit/s與32kbit/s WAV音頻文件。通過(guò)示波器測(cè)量的模擬輸出如圖6所示,可以看出明顯的包絡(luò)信號(hào)。通過(guò)以上結(jié)論可以看出,系統(tǒng)可以充分利用FPGA 片內(nèi)資源,從而減少對(duì)板內(nèi)面積占用并減低系統(tǒng)功耗,也易于移植入同類的嵌入式系統(tǒng)中。

在本文的基礎(chǔ)上,可以進(jìn)一步發(fā)揮FPGA的靈活性,比如在開(kāi)發(fā)FPGA上支持PCI從設(shè)備DMA模式,以進(jìn)一步加強(qiáng)PCI總線的讀寫(xiě)效率、I2S總線的右對(duì)齊和DSP模式等,并且可以開(kāi)發(fā)語(yǔ)音芯片上的語(yǔ)音采集功能,使系統(tǒng)實(shí)現(xiàn)語(yǔ)音采集、轉(zhuǎn)換、傳輸?shù)裙δ堋?/div>

推薦閱讀:

推薦閱讀: