【導(dǎo)讀】某接地臺(tái)式產(chǎn)品,對接地端子處進(jìn)行測試電壓為6KV的ESD接觸放電測試時(shí),系統(tǒng)出現(xiàn)復(fù)位現(xiàn)象。測試中嘗試將接地端子與內(nèi)部數(shù)字工作地相連的 Y電容斷開,測試結(jié)果并未明顯改善。

[現(xiàn)象描述]

某接地臺(tái)式產(chǎn)品,對接地端子處進(jìn)行測試電壓為6KV的ESD接觸放電測試時(shí),系統(tǒng)出現(xiàn)復(fù)位現(xiàn)象。測試中嘗試將接地端子與內(nèi)部數(shù)字工作地相連的 Y電容斷開,測試結(jié)果并未明顯改善。

[原因分析]

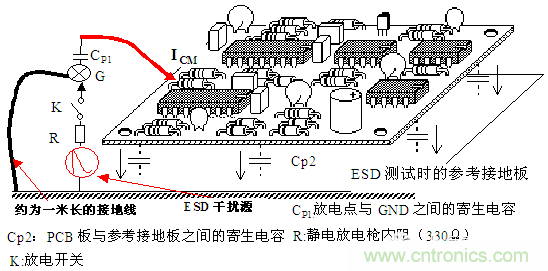

ESD干擾進(jìn)入產(chǎn)品內(nèi)部電路,形式多種多樣。對于本案例中的被測產(chǎn)品來說,其測試點(diǎn)為接地點(diǎn),大部分的ESD干擾能量將從接地線流走, 也就是說ESD電流并沒有直接流入該產(chǎn)品的內(nèi)部電路,但是,處在IEC61000-4-2標(biāo)準(zhǔn)規(guī)定的ESD測試環(huán)境中的這個(gè)臺(tái)式設(shè)備,其接地線長度在1m左右,該接地線將產(chǎn)生較大的接地引線電感(可以用1u H/m來估算),在靜電放電干擾發(fā)生時(shí)(即圖1中開關(guān)K閉合時(shí)),高的頻率(下于1ns的上升沿)靜電放電電流并不能使該被測產(chǎn)品接地點(diǎn)上的電壓為零(即圖1 中G點(diǎn)的電壓在K閉合時(shí)并不為零)。這個(gè)在接地端子上不為零電壓將會(huì)進(jìn)一步進(jìn)入產(chǎn)品內(nèi)部電路。圖1已經(jīng)給出了ESD干擾進(jìn)入產(chǎn)品內(nèi)部PCB的原理圖。

圖 1 ESD干擾進(jìn)入產(chǎn)品內(nèi)部PCB的原理圖

從圖1中還可以看出,CP1:(放電點(diǎn)與GND之間的寄生電容),Cp2:(PCB板與參考接地板之間的寄生電容),PCB板的工作地(GND)和靜電放電槍(包括靜電放電槍接地線)一起形成了一條干擾通路,干擾電流為ICM。在這條干擾路徑中,PCB板處在其中,顯然PCB在此時(shí)受到了靜電放電的干擾。 如果該產(chǎn)品還存在其它電纜,這種干擾將更為嚴(yán)重。

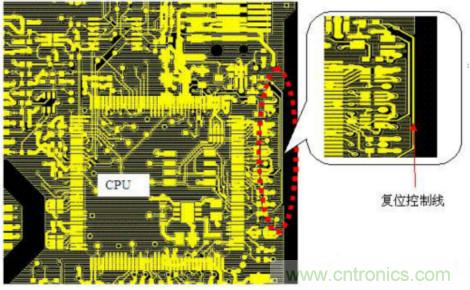

干擾是如何導(dǎo)致被測產(chǎn)品復(fù)位的呢,經(jīng)過仔細(xì)檢查被測產(chǎn)品的PCB之后發(fā)現(xiàn),該P(yáng)CB板中CPU的復(fù)位控制線布置在PCB板的邊緣,并且在GND平面之外,如圖2所示。

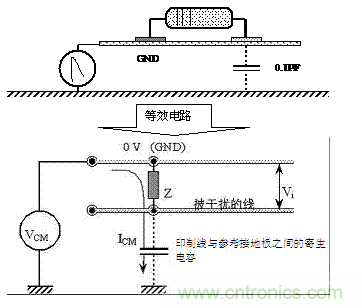

再來解釋一下為何布置在PCB邊緣的印制線比較容易受到干擾,那應(yīng)該從PCB板中的印制線與參考接地板之間的寄生電容談起。印制線與參考接地板之間存在寄生電容,這個(gè)寄生電容將使PCB板中的印制信號線受到干擾,共模干擾電壓干擾PCB中印制線原理圖如圖3所示。

從圖3可以看出,當(dāng)共模干擾(相對與參考接地板的共模干擾電壓)進(jìn)入GND后,會(huì)在PCB板中的印制線和GND之間產(chǎn)生一個(gè)干擾電壓,這個(gè)干擾電壓不但與印制線與PCB板GND之間的阻抗(圖3中的Z)有關(guān)還有PCB中印制線與參考接地板之間的寄生電容有關(guān)。

假設(shè)印制線與PCB板GND之間的阻抗Z不變,則,當(dāng)印制線與參考接地板之間的寄生電容越大時(shí),在印制線與PCB板GND之間的干擾電壓Vi越大,這個(gè)電壓與PCB中的正常工作電壓相疊加,將直接影響PCB中的工作電路。

圖2 被測產(chǎn)品局部PCB布線實(shí)圖

圖3 共模干擾電壓干擾PCB中印制線原理圖

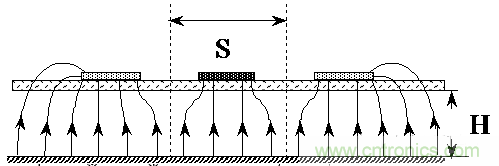

由印制線與參考接地板之間的寄生電容計(jì)算公式1 可知,印制線與參考接地板之間的寄生電容大小取決于印制線與參考接地板之間的距離(即公式1中的H)和印制線與參考接地板之間形成電場的等效面積(即公式1中的S)。

Cp ≈ 0.1 x S / H (1)

Cp : 寄生電容 [pF]

S : 印制線等效面積 [cm2]

H : 高度 [cm]

當(dāng)印制線布置在PCB板邊緣時(shí),該印制線與參考接地板之間將形成相對較大寄生電容,因?yàn)椴贾迷赑CB內(nèi)部的印制線與參考接地板之間形成的電場被其它印制線所“擠壓”,而布置在邊緣的印制線與參考接地板之間形成的電場且相對比較發(fā)散。圖4為印制線與參考接地板之間電場分布示意圖。

圖4 印制線與參考接地板之間電場分布示意圖

顯然,對于本案例中的電路設(shè)計(jì),由于PCB中的復(fù)位信號線布置在PCB板的邊緣并且已經(jīng)落在GND平面之外,因此復(fù)位信號線會(huì)受到較大的干擾,導(dǎo)致ESD測試時(shí),系統(tǒng)出現(xiàn)復(fù)位現(xiàn)象。

【處理措施】

根據(jù)以上的原理分析,很容易得出以下兩種處理措施:

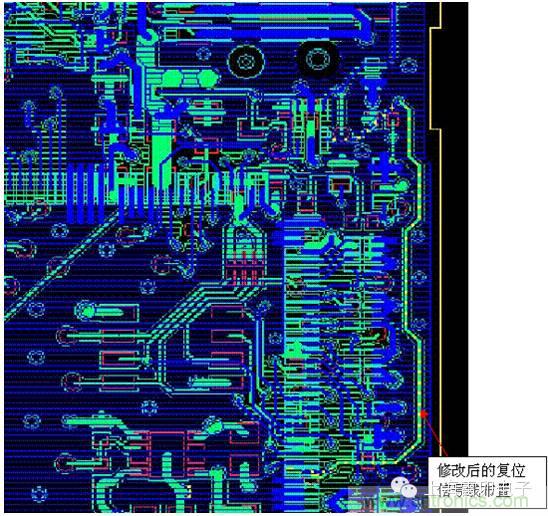

1、 重新進(jìn)行PCB布線,將復(fù)位信號印制線在PCB上左移,使其在GND平面覆蓋的區(qū)域內(nèi),而且遠(yuǎn)離PCB板邊緣,同時(shí)為了進(jìn)一步降低復(fù)位信號印制線與參考接地板時(shí)間的寄生電容,可以在復(fù)位信號印制線所在的層(本案例為4層板,復(fù)位信號線布置在表層)上空余的地方鋪上GND銅箔(通過大量過孔與相鄰GND平面相連),如圖5所示。

圖5 修改后的復(fù)位信號線布置PCB實(shí)圖

2、在受干擾的復(fù)位印制線上,靠近CPU復(fù)位管腳的附近并聯(lián)一個(gè)電容,電容值可以選在100pf~1000pf之間。

推薦閱讀: