【導(dǎo)讀】高速模數(shù)轉(zhuǎn)換器(ADC)存在一些固有限制,使其偶爾會在其正常功能以外產(chǎn)生罕見的轉(zhuǎn)換錯誤。但是,很多實際采樣系統(tǒng)不容許存在高ADC轉(zhuǎn)換誤差率。因此,量化高速模數(shù)轉(zhuǎn)換誤差率(CER)的頻率和幅度非常重要。

高速或GSPS ADC(每秒千兆采樣ADC)相對稀疏出現(xiàn)的轉(zhuǎn)換錯誤不僅造成其難以檢測,而且還使測量過程非常耗時。該持續(xù)時間通常超出毫秒范圍,達到幾小時、幾天、幾周甚至是幾個月。為了幫助消減這一耗時測試負擔,可以在一定“置信度”的確定性情況下估算誤差率,而仍然保持結(jié)果的質(zhì)量。

誤碼率(BER)與轉(zhuǎn)換誤差率

與串行或并行數(shù)字數(shù)據(jù)傳輸中BER的數(shù)字等效值類似,CER是轉(zhuǎn)換錯誤數(shù)與樣本總數(shù)之比。但是,BER和CER之間有一些截然不同之處。數(shù)字數(shù)據(jù)流中的BER測試采用長偽隨機序列,該序列可于發(fā)送器中在傳輸兩端使用常用種子值來啟動。接收器預(yù)期將收到理想的傳輸。通過觀察接收數(shù)據(jù)與理想數(shù)據(jù)的差異,便可精確計算出BER。兩端之間偽隨機序列數(shù)據(jù)中的失配(基于種子值)即視為誤碼。

與CER不同,誤差測定不像純數(shù)字比較那么簡單。由于ADC轉(zhuǎn)換過程中始終具有小的非線性,另外還存在系統(tǒng)噪聲和抖動,因此并非總是能確定預(yù)期數(shù)據(jù)和實際數(shù)據(jù)之間的確切差異。相反,需要建立誤差閾值,用于確定轉(zhuǎn)換錯誤和具有容許預(yù)期噪聲的樣本之間的界限。這與數(shù)字BER不同,并不會對發(fā)送和接收的預(yù)期數(shù)據(jù)進行確切比較。相反,首先必須量化樣本的誤差幅度,然后再確定是轉(zhuǎn)換錯誤,還是在轉(zhuǎn)換器和系統(tǒng)的預(yù)期非線性范圍內(nèi)。ADC后端數(shù)字接口的誤碼率必須低于轉(zhuǎn)換器的內(nèi)核CER,因此無法忽視。如果并非如此,那么數(shù)據(jù)輸出傳輸誤差將覆蓋CER并成為主要誤差來源。

亞穩(wěn)態(tài)

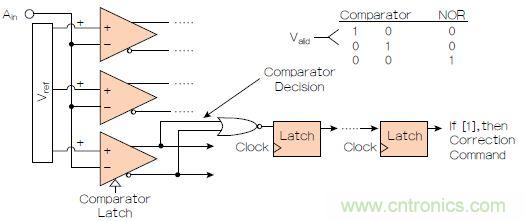

高速ADC中造成轉(zhuǎn)換錯誤的一個常見原因是一種稱為亞穩(wěn)態(tài)的現(xiàn)象。高速ADC在將模擬信號轉(zhuǎn)換為數(shù)字值的轉(zhuǎn)換過程中,往往會在不同階段使用多個梯級比較器。如果比較器無法確定模擬輸入是高于還是低于其參考點時,就會產(chǎn)生可能導(dǎo)致出現(xiàn)錯誤代碼的亞穩(wěn)態(tài)結(jié)果。當兩個比較器的輸入之差幅度非常小或為零時,就可能發(fā)生這種情況,此時無法進行正確比較。由于此錯誤值會沿著流水線傳播,因此ADC可能產(chǎn)生重大的轉(zhuǎn)換錯誤。

當差分模擬輸入為相對較大的正值或負值時,比較器可以快速計算出差值并給出明確決定。當差分值很小或為零時,比較器做出決定所需的持續(xù)時間會長很多。如果在此決定點之前比較器輸出鎖存,則將產(chǎn)生亞穩(wěn)態(tài)結(jié)果。

有些設(shè)計方案可以減輕這個問題。首先,將比較器的不確定范圍設(shè)計的非常小,迫使比較器在可能的最大模擬輸入條件范圍內(nèi)做出準確決定。但是,這可能造成電路功率和設(shè)計尺寸增加。

第二種方法是盡量延遲比較器采樣時間,給模擬輸入最長的時間建立至已知的比較器輸出值。但這種方法存在多個限制,因為延遲最長也只能持續(xù)到當前采樣時間結(jié)束,而后比較器必須繼續(xù)處理下一次采樣。第三種方法是采用智能錯誤檢測和校正算法,該算法會對比較器在高速ADC轉(zhuǎn)換過程后續(xù)階段中引入的不確定性進行數(shù)字補償。當比較器未能在最大允許時間內(nèi)做出決定時,邏輯可檢測到該缺失。然后,此信息可被附加到相關(guān)樣本上,以便未來進行內(nèi)部調(diào)整。識別出此警報時,可使用后處理步驟在樣本從轉(zhuǎn)換器輸出前糾正該錯誤。這可以從圖1中的AD9625看出,它是ADI公司的一款12位、2.5GSPS ADC。

圖1:可在AD9625的模數(shù)轉(zhuǎn)換過程內(nèi)識別比較器的不確定性。在后續(xù)步驟中執(zhí)行校正命令以校正樣本,然后再從轉(zhuǎn)換器輸出。

置信度

CER置信度(CL)是指在不精確到特定故障率的情況下對未來錯誤的外推預(yù)期。這可減少針對給定CER獲取的樣本總數(shù),但代價是不能保證100%的確定性。從數(shù)學角度來說,要達到絕對100%的確定性,需要取得無限持續(xù)時間內(nèi)的樣本。因此,根據(jù)行業(yè)經(jīng)驗,95%的置信度已經(jīng)相當接近已知值,并且實現(xiàn)了不確定性和測量時間之間的平衡。如果將測試重復(fù)一百次,則有95次可以準確識別誤碼率。有時工程師會誤認為一旦在測試期間檢測到誤差,該過程就會結(jié)束并找到最終的CER。這既不準確也不完整。無論過程中是否有誤差,轉(zhuǎn)換誤差率及相關(guān)的置信度都可以測試。但是,如果在給定置信度下檢測到誤差,則與沒有錯誤時的樣本數(shù)相比,必須增加測量的樣本數(shù)量。

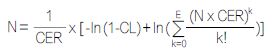

以上公式給出了置信度、誤碼率和樣本數(shù)之間的自然對數(shù)數(shù)學關(guān)系表達式。式中:N為測量的樣本數(shù);CER為轉(zhuǎn)換誤碼率;CL為置信度;E為檢測到的錯誤數(shù)。

未檢測到誤差時,公式有所簡化,右邊的項等于零,結(jié)果僅取決于左邊的項。當CL為95%且未檢測到誤差時,所需的樣本數(shù)僅約為預(yù)期CER的倒數(shù)乘以3。測量到100%置信度,即對于任何CER值都有CL=1.0,從數(shù)學角度上需要獲取-ln(0)無窮大的無限樣本數(shù)(N)。

誤差閾值

高速ADC中的轉(zhuǎn)換誤差幅度很關(guān)鍵,有些誤差比其他誤差更重要。例如,一個或兩個最低有效位(LSB)誤差可能在系統(tǒng)的預(yù)期噪底之內(nèi),甚至可能不會影響瞬時性能。但是,最高有效位(MSB)誤差,乃至滿量程誤差可能造成系統(tǒng)故障事件。因此,CER測試需要具有一種機制或閾值來確定轉(zhuǎn)換中誤差的嚴重程度。

轉(zhuǎn)換的誤差閾值應(yīng)該包括ADC的已知線性不足,以及時鐘抖動和其他超出轉(zhuǎn)換器功能的系統(tǒng)噪聲。對于任何給定樣本,這些通常會累加為14位ADC的4或5個最低有效位(LSB)或16~32個代碼。根據(jù)ADC分辨率、系統(tǒng)性能和應(yīng)用的誤碼率要求,該值的大小可能略有不同。使用此誤差帶與理想值進行比較后,超出此限值的樣本將被視為轉(zhuǎn)換錯誤。在傳統(tǒng)視頻ADC中,此錯誤被稱為“閃碼”,因為它會在視頻屏幕上產(chǎn)生亮白色像素閃爍??山邮艿霓D(zhuǎn)換器誤碼率很大程度上取決于信號處理系統(tǒng)和系統(tǒng)誤差容差要求。

歷史上測量的GSPS ADC轉(zhuǎn)換誤差率一般不會低于1e-14。1e-15的誤差率意味著轉(zhuǎn)換器在1e15個樣本范圍內(nèi)不應(yīng)出現(xiàn)轉(zhuǎn)換錯誤。雖然這些數(shù)字看起來很大,但憑借當今先進轉(zhuǎn)換器技術(shù)的高采樣速率,對于CER測試仍然可以實現(xiàn)。但是,對于具有8ns采樣速率的125MSPS轉(zhuǎn)換器,1e15次采樣將占用800,000s(1e15*8ns),也即9.24天。要在這些誤碼率中實現(xiàn)95%的CL,則需要分別將這些采樣持續(xù)時間的均乘以2.996。

CER測試

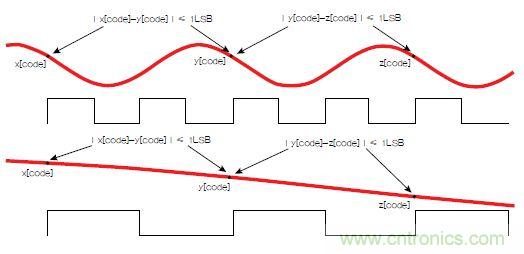

圖2給出了如何測試內(nèi)部ADC 內(nèi)核的CER。在或接近ADC最大編碼速率下采樣時,可使用頻率相對較慢的正弦波作為模擬輸入。應(yīng)對模擬輸入信號進行規(guī)劃,以便在忽視系統(tǒng)噪聲的情況下,兩個相鄰樣本之間的預(yù)期絕對差不大于1LSB代碼。理想情況下,模擬輸入信號比滿量程稍大,以便運用ADC的所有代碼。應(yīng)計算模擬輸入和編碼采樣速率,以便建立較長的一致性周期,而ADC不在同一代碼級別進行一致采樣。

圖2:CER測試的兩種采樣情形。頂部的情形是以比Fs/2稍快的速率對模擬信號進行采樣,其中僅每隔一個樣本比較一次。理想情況下,兩個連續(xù)樣本的不同之處不超過一個LSB代碼。下面的情形是對相對較慢的模擬輸入進行過采樣,以便兩個相鄰樣本的不同之處也不超過一個LSB代碼。

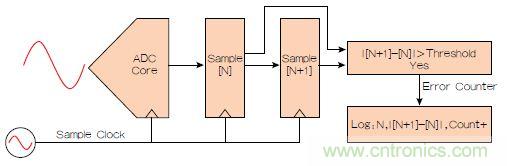

圖3:CER測試比較兩個連續(xù)ADC樣本和預(yù)定誤差閾值。計數(shù)器記錄錯誤發(fā)生次數(shù)、幅值和采樣位置標識符。

系統(tǒng)使用一個計數(shù)器來跟蹤兩個相鄰樣本之間的幅度差值超過閾值限值的情況,并將這種情況計數(shù)為轉(zhuǎn)換錯誤。該計數(shù)器必須保留整個測試過程中錯誤的累加總數(shù)。為了保證系統(tǒng)按預(yù)期工作,還應(yīng)記錄誤差幅度與理想情況之間的關(guān)系。測試需要的時間將基于采樣速率、所需的測試CER和所需的置信度(圖3)。

小結(jié)

典型轉(zhuǎn)換器架構(gòu)可實現(xiàn)一些系統(tǒng)可接受的測量轉(zhuǎn)換誤碼率,新的設(shè)計和錯誤檢測算法正推動限值實現(xiàn)更佳的性能。ADI的12位2.5GSPS ADC AD9625分級比較型流水線內(nèi)核使用專有技術(shù)檢測流水線處理前期的ADC轉(zhuǎn)換錯誤,然后處理和糾正后期的錯誤。這在12位GSPS ADC上實現(xiàn)了優(yōu)于1e-15、置信度為95%的行業(yè)一流測量CER。

免責聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請聯(lián)系小編進行處理。

推薦閱讀: