【導(dǎo)讀】C2000 Gen-3對(duì)比于Gen-2的C2000,加入了三角函數(shù)運(yùn)算單元來進(jìn)一步提升運(yùn)算能力,提供了更多的ADC模塊及窗口比較器來增強(qiáng)采樣和保護(hù)的快速性和靈活性。同時(shí),在實(shí)時(shí)通信方面,引入了新一代快速串行通信接口Fast Serial Interface (FSI),可以支持在隔離的情況下最高200Mbps的數(shù)據(jù)傳輸速率。

本文主要討論ADC通道的選擇、FSI接口的應(yīng)用、3.3V供電選型考量、GPIO口的配置和JTAG的連接與調(diào)試進(jìn)行詳細(xì)介紹。

1. ADC通道的輸入寄生電容:

當(dāng)我們?cè)诎淹獠啃盘?hào)匹配到C2000的ADC通道的時(shí)候,常常會(huì)忽略到ADC的輸入模型可能會(huì)帶來的潛在影響。其中最為明顯的就是每個(gè)ADC通道上都會(huì)有一個(gè)輸入寄生電容,而具有較大輸入寄生電容的ADC通道通常是不適用于高頻采樣信號(hào)的。這是因?yàn)檩^大的輸入寄生電容會(huì)帶來更長(zhǎng)的采樣窗口,進(jìn)而可能會(huì)影響到控制回路里的Computational power budget。如需了解更多信息,請(qǐng)參照 F28002X TRM的Choosing an Acquisition Window Duration 章節(jié)。

針對(duì)于Gen-3的F28002X的C2000, 我們可以在數(shù)據(jù)手冊(cè)的ADC Input Model章節(jié)的表格Table 1 中查詢到每一個(gè)ADC通道的內(nèi)部輸入寄生電容?;赥able 1,ADCINA3/ADCINC5通道不管是否啟用了比較器,因?yàn)槠鋬?nèi)部輸入寄生電容達(dá)到71.4pF,都是明顯是不適合用于高速采樣信號(hào)的。而對(duì)于ADCINA0/ADCINC15來說,如果使用了內(nèi)部比較器,那么就需要慎重考慮采樣窗口和外部采樣電路。例如:如果我們希望使用某個(gè)ADC通道實(shí)現(xiàn)OVP功能的實(shí)現(xiàn),而我們又只剩下了ADCINA0/ADCINC15這一個(gè)通道,那么我們可以利用軟件代碼在后臺(tái)任務(wù)來實(shí)現(xiàn)OVP的功能,而無需使用內(nèi)部比較器。如果我們一定要實(shí)現(xiàn)基于CMPSS模塊的OVP功能,那么建議切換到其他到ADC通道。

Table 1: ADC 通道寄生電容

2. FSI 接口介紹:

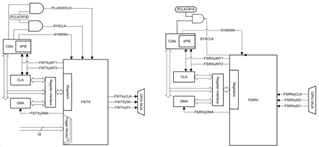

FSI接口是Gen-3的C2000引入的最新的高速可靠的快速串行接口。針對(duì)需要隔離的通信應(yīng)用場(chǎng)景,F(xiàn)SI接收端模塊具有一個(gè)可編程的Delay Line Control。通過對(duì)每一個(gè)線的RX_DLY_LINE_CTRL寄存器值進(jìn)行修改,從而對(duì)系統(tǒng)元器件(例如信號(hào)緩沖器和隔離器等)引起的信號(hào)延遲和板級(jí)的(例如不均勻的布線等)引起的信號(hào)延遲進(jìn)行補(bǔ)償,最終保證信號(hào)的完整性,實(shí)現(xiàn)高速可靠通信。FSI是應(yīng)用于點(diǎn)對(duì)點(diǎn)的的通信協(xié)議,例如單主/單從配置,所以FSI主要應(yīng)用于以下兩種場(chǎng)景:

● 兩個(gè)MCU直接進(jìn)行通信

● 板級(jí)之間的通信,例如PSFB的原邊和副邊的兩個(gè)MCU通過隔離芯片來通信

FSI接口的傳輸端(FSITX)和接收端(FSIRX)是完全獨(dú)立的,每個(gè)端口有自己獨(dú)立的寄存器、時(shí)鐘和中斷。而不同于IIC接口的一個(gè)重要區(qū)別是其只能作為單一方向的通信傳輸?;贔igure 1, FSI的每個(gè)端口有3個(gè)信號(hào)線,分別是時(shí)鐘CLK,數(shù)據(jù)線D0和一個(gè)額外的數(shù)據(jù)線D1。額外的數(shù)據(jù)線D1是作為多線傳輸來加倍數(shù)據(jù)傳輸速率,也可作為GPIO口。所以,通常來說點(diǎn)對(duì)點(diǎn)的FSI需要至少4根信號(hào)線。FSI最大可支持的時(shí)鐘頻率為50MHz,而時(shí)鐘的上升沿和下降沿也可作為數(shù)據(jù)的有效位判定。所以,理論上是可以達(dá)到最高200Mbps的傳輸速率。

Figure 1: FSITX/RX 模塊連接圖

在電機(jī)驅(qū)動(dòng)和數(shù)字電源中,MCU之間進(jìn)行實(shí)時(shí)通信越來越普遍,而這也對(duì)通信實(shí)時(shí)性的要求變高。FSI接口因?yàn)榫哂锌删幊痰膁elay line control,可以確保隔離應(yīng)用場(chǎng)景下高速通信且可靠,所以對(duì)比傳統(tǒng)的UART、SPI和CAN等通信接口來說更具優(yōu)勢(shì)。

F28002X FSI 和IIC兼容GPIO口及隔離芯片:

如果我們要把F280025C 64pin作為副邊的MCU和原邊的MCU進(jìn)行FSI通信,在工程師進(jìn)行系統(tǒng)調(diào)試階段,有時(shí)會(huì)希望通信接口既能作為FSI又能作為IIC通信。這個(gè)時(shí)候就會(huì)引入一些問題,例如IIC是雙向通信,而FSI是單向的。針對(duì)F280025C 64pin,只有以下GPIO口既能支持FSI,又能支持IIC:

● GPIO33 >> I2CA_SCL and FSIRXA_CLK

● GPIO8 >> I2CA_SCL and FSITXA_D1

● GPIO0 >> I2CA_SDA and FSIRXA_CLK

● GPIO32 >> I2CA_SDA and FSIRXA_D0

● GPIO10 >> I2CA_SDA and FSITXA_CLK

首先,只有GPIO32是支持FSIRXA_D0的數(shù)據(jù)線。其次,只有GPIO33的FSI和IIC都是作為時(shí)鐘使用。所以我們建議使用GPIO32/33作為接收端(RX)的數(shù)據(jù)和時(shí)鐘線。

此外,在選擇隔離器時(shí),如果我們已經(jīng)明確了通信方向,那么只要我們保持IIC和FSI的數(shù)據(jù)傳輸方向,那么依然可以使用單向的隔離器,例如ISO7742來傳輸數(shù)據(jù)。

3. 3V供電電源芯片選擇小細(xì)節(jié):

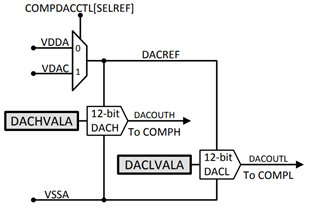

通常我們根據(jù)C2000的供電VDDA/VDDIO選擇對(duì)應(yīng)的前級(jí)DC/DC或者LDO時(shí),更多會(huì)把重點(diǎn)放在輸出電流能力、PSRR和壓降等參數(shù)上,往往忽視了LDO的精度可能會(huì)帶來的影響。針對(duì)C2000內(nèi)部CMPSS模塊的參考DAC模塊,系統(tǒng)框圖如下圖。如果我們選擇VDDA作為COMPDAC的參考電壓,那么VDDA的任意百分比變化都會(huì)影響到COMPDAC的輸出。所以通常針對(duì)峰值電流控制模式的DC/DC,推薦使用1%精度的LDO,例如TPS7A90。

Figure 2: C2000 CMPSS 模塊的參考DAC部分框圖

4. GPIO口與外部信號(hào)的匹配:

● 三態(tài)(Tri-state)外部信號(hào)。例如外部信號(hào)Active的時(shí)候需要拉高,Sleep狀態(tài)下需求拉低,IDLE模式需求Floating。那么我們有兩種方式來處理,第一是通過將GPIO設(shè)置為輸入,然后禁用上拉,第二種是將GPIO設(shè)置為輸出和開漏,同時(shí)把GPIO電平設(shè)為低位。而這都可以通過C2000里面的GPAODR寄存器實(shí)現(xiàn)。

● 特定情況下,一些例如使能的數(shù)字口,如果不足以在低電平拉低,可以把其配置到模擬口。然后通過軟件對(duì)模擬量的判斷來實(shí)現(xiàn)高低電平的判斷,從而實(shí)現(xiàn)使能和關(guān)閉使能。

數(shù)字GPIO口不夠時(shí)的備選方案:

● 將原本作為風(fēng)扇等其他小型設(shè)備的反饋電壓(原邊為數(shù)字信號(hào))作為模擬GPIO口。然后通過軟件代碼基于采樣電壓來判斷高低電平。

● Boot load的GPIO24和GPIO32如果是boot from flash,可以節(jié)省出兩個(gè)GPIO口。如果是boot from SCI和CAN等的話,可以在boot結(jié)束后復(fù)用為其他GPIO口。

5. JTAG接口連接及調(diào)試:

通常來說JTAG(IEEE標(biāo)準(zhǔn) 1149.1-1990 Standard Test Access Port and Boundary Scan Architecture) 具有五個(gè)引腳:

TMS/TDI/TDO/TCK/TRSTn。主要的三大功能如下:

● 下載軟件到MCU的Flash

● 調(diào)試

● 邊界掃描:訪問芯片內(nèi)部的信號(hào)邏輯狀態(tài)以及芯片引腳狀態(tài)等

通常針對(duì)JTAG連接出現(xiàn)問題的調(diào)試流程如下:

a) Power Good LED 開啟:TI所有的C2000開發(fā)板都有LED來標(biāo)識(shí)MCU的供電是否正常。

b) 檢查Device Manager:使用JTAG仿真器和PC通信,我們首先需要安裝好驅(qū)動(dòng)文件。通常我們?cè)诎惭bCCS的時(shí)候會(huì)有具體細(xì)節(jié)。如需驗(yàn)證驅(qū)動(dòng)是否成功安裝,連接JTAG模擬器到PC并供電。然后在PC的Control Panel >> Device Manger 來定位到USB仿真器。

Figure 3: Device Manager 驅(qū)動(dòng)確認(rèn)

c) 檢查MCU JTAG的TRSTn信號(hào)是否拉高:如果在CCS連接過程中,TRSTn沒有改變狀態(tài),那么需要驗(yàn)證仿真器是否配置正常。

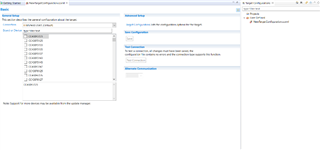

d) 檢查Target Configuration:在Target Configuration File (.ccxml) 會(huì)包含連接Target device的所有相關(guān)信息以及JTAG仿真器的類型。在CCS中點(diǎn)擊“View”,然后點(diǎn)擊Target Configuration,找到User Defined下的 .ccxml 文件,就會(huì)顯示處New Target Configuration 界面如下圖。在下圖中選擇合適的Devices,保持配置,再點(diǎn)擊測(cè)試連接即可測(cè)試連接是否正常。

Figure 4: Target Configuration 確認(rèn)連接是否正常

e) 啟動(dòng)CCS調(diào)試。

f) 檢查XRSn狀態(tài):如果XRSn的狀態(tài)是低或者出現(xiàn)從低到高再到低的脈沖狀態(tài),那么可能是多種因素造成。例如如果是從低到高再到低的脈沖,那么可能是看門狗導(dǎo)致的重啟。如果一直處于低電平,那么可能是因?yàn)楣╇娀蛘逷CB的其他的原因?qū)е铝薆rown Out Rest (BOR)。

g) 檢查Boot Mode:如果使用的是GPIO24和GPIO32默認(rèn)的Bootload口,那么參照F28002X的TRM中3章節(jié),檢查GPIO24和GPIO32的引腳來確認(rèn)是否在期望的Boot load 模式。

h) 檢查VREG/時(shí)鐘/系統(tǒng)時(shí)鐘:測(cè)量并確認(rèn)JTAG的時(shí)鐘和晶振是否符合數(shù)據(jù)手冊(cè)表明。測(cè)量并確認(rèn)是否供電是否運(yùn)行在了推薦電壓值以外導(dǎo)致了BOR等問題。

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請(qǐng)聯(lián)系小編進(jìn)行處理。

推薦閱讀: