【導(dǎo)讀】本文將討論匹配元器件及其互連, 并在選擇變壓器或巴倫,以及涉及到應(yīng)用連接配置技巧時重點關(guān)注關(guān)鍵規(guī)格。最后,將提供一些思路和優(yōu)化技巧,說明在GHz區(qū)域工作的DAC如何實現(xiàn)寬帶平滑阻抗變換。

今天,對于新IC元器件和技術(shù)的需求依然以令人吃驚的速度增長。商業(yè)和國防工業(yè)是需求增長的主要刺激因素。目前涉及半導(dǎo)體行業(yè)的大部分新規(guī)格都圍繞著降低尺寸(size)、重量(weight)和功耗(power)而展開——即SWaP。在半導(dǎo)體行業(yè),我們通過不斷改進的技術(shù)以及更巧妙的設(shè)計來滿足這些要求。然而,性能也是關(guān)鍵需求,尤其是GSPS領(lǐng)域的數(shù)模轉(zhuǎn)換器(DAC)技術(shù)。為了跟上這一步伐,人們常常忽略了關(guān)鍵的模擬輸出匹配網(wǎng)絡(luò)。

為了提供更高的清晰度,通常認(rèn)為高頻是超過1 GHz的頻率,高速是超過1 GSPS的速度;更重要的是,最終用戶可能會在DAC之后集成一個放大器,因此可用信號便不那么依賴于信號電平,而更多地依賴噪聲和保真度。本文將討論匹配元器件及其互連, 并在選擇變壓器或巴倫,以及涉及到應(yīng)用連接配置技巧時重點關(guān)注關(guān)鍵規(guī)格。最后,本文將提供一些思路和優(yōu)化技巧,說明在GHz區(qū)域工作的DAC如何實現(xiàn)寬帶平滑阻抗變換。

背景信息

DAC用途廣泛,最常見的用途包括:商業(yè)和軍事通信中的高頻復(fù)雜波形生成、無線基礎(chǔ)設(shè)施、自動測試設(shè)備(ATE)以及雷達和軍用干擾電子產(chǎn)品。 系統(tǒng)架構(gòu)師找到合適的DAC后,必須考慮輸出匹配網(wǎng)絡(luò),以保持信號結(jié)構(gòu)。元件選型和拓撲較之從前更為重要,因為GSPS DAC應(yīng)用要求工作在超奈奎斯特頻率下,此時所需的頻譜信息位于第二、第三或第四奈奎斯特區(qū)。

預(yù)備知識

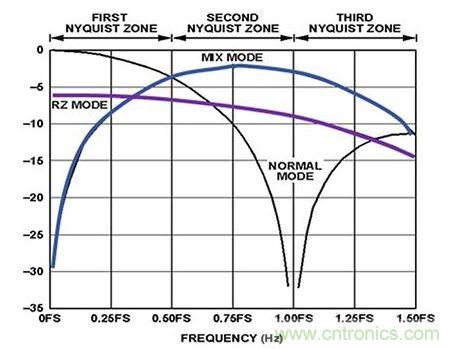

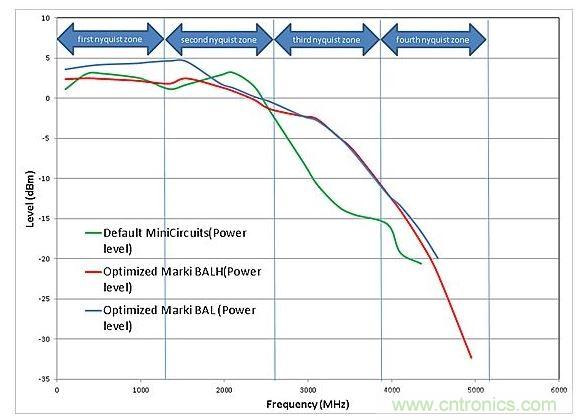

首先讓我們來考察DAC的作用,及其在信號鏈中的位置。DAC的作用很像信號發(fā)生器。 它能在中心頻率(Fc)范圍內(nèi)為復(fù)雜波形提供單音。以前,F(xiàn)c最大值位于第一奈奎斯特區(qū)中,或者為采樣頻率的一半。較新的DAC設(shè)計具有內(nèi)部時鐘倍頻器,可以有效地倍增第一奈奎斯特區(qū);可將其稱為“混頻模式”操作。使用混頻模式的DAC自然輸出頻率響應(yīng)具有sinX/e^(X^2)曲線的形狀,如圖1所示。

系統(tǒng)架構(gòu)師可參考產(chǎn)品數(shù)據(jù)手冊,了解元器件性能。很多時候,諸如功率水平和無雜散動態(tài)范圍(SFDR)等性能參數(shù)會給出多種頻率下的數(shù)值。明智的系統(tǒng)設(shè)計人員可將同一個DAC應(yīng)用于上文所述的超奈奎斯特區(qū)中。值得注意的是,在較高頻率下(或較高區(qū)域中)預(yù)期輸出電平將會低得多,因此很多信號鏈會在DAC之后集成一個額外的增益模塊或驅(qū)動放大器,以補償該損耗。

圖1: DAC Sinx/x輸出頻率響應(yīng)與混頻模式的關(guān)系

元器件方面的考慮,如選擇輸出巴倫

只有最終用戶設(shè)計和測得的最佳性能GSPS DAC才是好器件。為了最大程度發(fā)揮高品質(zhì)DAC的性能,應(yīng)當(dāng)只選用最好的元器件。必須在一開始就作出重要的電路決定。 數(shù)據(jù)手冊上的DAC性能是否提供了足夠的輸出功率?是否需要有源器件?信號鏈?zhǔn)欠裥枰獜腄AC差分輸出傳送至單端環(huán)境?是否需要用到變壓器或巴倫?巴倫的合適阻抗比是多少?本文將重點討論巴倫或變壓器的使用。

選擇巴倫時,應(yīng)仔細考慮相位和幅度不平衡1。阻抗比(即電壓增益)、帶寬、插入損耗和回損同樣也是重要的性能考慮因素。 采用巴倫進行設(shè)計并不總是簡單明了。例如,巴倫的特性隨頻率而改變,這會給預(yù)期蒙上陰影。有些巴倫對接地、布局布線和中心抽頭耦合敏感。

系統(tǒng)設(shè)計人員不應(yīng)完全根據(jù)巴倫數(shù)據(jù)手冊上的性能作為器件選擇的唯一基礎(chǔ)。經(jīng)驗在這里能夠發(fā)揮巨大作用:存在PCB寄生效應(yīng)時,巴倫以新的形式構(gòu)成外部匹配網(wǎng)絡(luò);轉(zhuǎn)換器的內(nèi)部阻抗(負載)同樣成為等式的一部分。

選擇巴倫時需注意的重要特性有很多,本文不作深入討論。

目前市場上,Anaren、Hyperlabs、Marki Microwave、MiniCircuits和Picosecond作為最佳解決方案,可提供最寬的帶寬。這些專利設(shè)計采用特殊拓撲,允許只采用單一器件實現(xiàn)千兆區(qū)域帶寬擴展,從而提供更高的平衡度。

使用單個巴倫或多個巴倫拓撲時,最后需要注意的一點是,布局對于相位不平衡同樣具有重要作用。 為在高頻下保持最佳性能,布局應(yīng)盡可能對稱。否則,走線輕微失配可能使采用巴倫的前端設(shè)計變得毫無用處,甚至使動態(tài)范圍受限。

[page]

輸出匹配

依賴頻率的元器件將會始終限制帶寬,如并聯(lián)電容和串聯(lián)電感。也就是說,考慮優(yōu)化而非匹配,可能更為有效。今天,巴倫的超寬帶寬幾乎不可能“配合”多倍頻程頻譜范圍。對以上參數(shù)的優(yōu)化則要求對系統(tǒng)的最終用途有深入的了解。例如,電路是否需要提供最大功率傳輸,而較少考慮SFDR?或者是否需要最高線性度設(shè)計,同時突出SNR和SFDR而較少考慮DAC的輸出驅(qū)動強度?這意味著在應(yīng)用中,應(yīng)當(dāng)權(quán)衡每個參數(shù)的重要性。

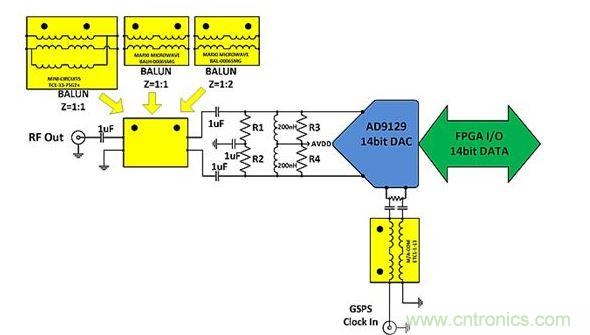

本例中,如圖2所示為AD9129 GSPS DAC輸出網(wǎng)絡(luò)。該網(wǎng)絡(luò)中的每個電阻和巴倫都可改變,然而隨著每個電阻值的變化,性能參數(shù)也會如表1所示發(fā)生改變。

圖2: AD9129 DAC輸出前端功能框圖

表1: 幾種情形的數(shù)據(jù)定義

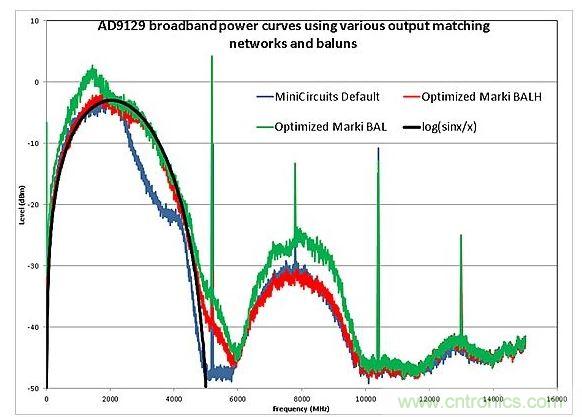

讀者需注意,最佳元器件值之間的差異非常小。巴倫元件具有最大的變化值。下文圖3中的數(shù)據(jù)顯示DAC寬帶噪聲輸出模式的優(yōu)化;DAC只是在全部可用頻譜帶寬中產(chǎn)生信號音。

最初的情形顯示第一奈奎斯特區(qū)的可用功率下降,而第二、第三和第四奈奎斯特區(qū)中極有可能出現(xiàn)混疊信號音。情形2顯示第一和第二奈奎斯特區(qū)中的輸出電平增加,以及較高奈奎斯特區(qū)中的可用功率下降。最后,情形3為最佳情況,看上去在第一和第二奈奎斯特區(qū)具有良好的輸出功率,同時相比情形1,區(qū)域3和4中的可用功率保持在最低水平。

圖3: 寬帶噪聲模式中的DAC性能

[page]

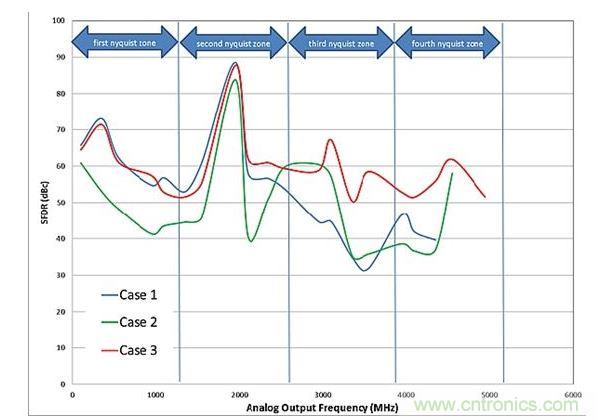

圖4和5顯示DAC為單音模式時的記錄數(shù)據(jù)。圖5顯示多個奈奎斯特區(qū)中不同頻率的輸出功率水平。 圖4顯示各種情形與DAC輸出頻率下的SFDR。讀者應(yīng)當(dāng)對參數(shù)規(guī)劃的權(quán)衡取舍有一個更全面的了解,因為隨著設(shè)計過程的展開,必須理解這些參數(shù)并對其優(yōu)化。 顯然,情形1可以通過替換為帶寬更寬的巴倫解決方案加以改進,即情形2。

在第二奈奎斯特區(qū)獲得更高的功率水平和更佳的SFDR。此外,情形3中采用1:2寬帶巴倫,則改進后的功率水平便得到了保持,同時進一步改進了系統(tǒng)的SFDR。其它重要發(fā)現(xiàn)有:在1900MHz附近存在SFDR的“最有效點”。該性能獨立于輸出元器件,這是因為DAC存在內(nèi)部阻抗。

圖4: SFDR性能對比

圖5: 輸出功率水平對比

結(jié)論

GSPS DAC的最新發(fā)展可讓設(shè)計人員在發(fā)射信號鏈上略過多個混頻級,直接處理所需的RF頻段。使用GSPS DAC時,必須仔細考慮輸出網(wǎng)絡(luò)。設(shè)計高速、高分辨率轉(zhuǎn)換器布局時,不容易照顧到所有的具體特性。從DAC輸出差分環(huán)境轉(zhuǎn)換至單端RF輸出時,必須特別注意巴倫的選擇。

另外,設(shè)計GSPS DAC輸出網(wǎng)絡(luò)時,必須注意網(wǎng)絡(luò)的布局與拓撲;走線寬度和長度是非常重要的參數(shù),需加以優(yōu)化。記住,為了“配合”特定應(yīng)用,需要滿足很多參數(shù)。