【導(dǎo)讀】接地?zé)o疑是系統(tǒng)設(shè)計(jì)中最為棘手的問(wèn)題之一。盡管它的概念相對(duì)比較簡(jiǎn)單�����,實(shí)施起來(lái)卻很復(fù)雜����,遺憾的是,它沒(méi)有一個(gè)簡(jiǎn)明扼要可以用詳細(xì)步驟描述的方法來(lái)保證取得良好效果��,但如果在某些細(xì)節(jié)上處理不當(dāng)��,可能會(huì)導(dǎo)致令人頭痛的問(wèn)題���。

對(duì)于線性系統(tǒng)而言��,"地"是信號(hào)的基準(zhǔn)點(diǎn)����。遺憾的是��,在單極性電源系統(tǒng)中���,它還成為電源電流的回路���。接地策略應(yīng)用不當(dāng),可能嚴(yán)重?fù)p害高精度線性系統(tǒng)的性能。

對(duì)于所有模擬設(shè)計(jì)而言�,接地都是一個(gè)不容忽視的問(wèn)題,而在基于PCB的電路中����,適當(dāng)實(shí)施接地也具有同等重要的意義。幸運(yùn)的是�����,某些高質(zhì)量接地原理��,特別是接地層的使用�����,對(duì)于PCB環(huán)境是固有不變的��。由于這一因素是基于PCB的模擬設(shè)計(jì)的顯著優(yōu)勢(shì)之一���,我們將在本文中對(duì)其進(jìn)行重點(diǎn)討論。

我們必須對(duì)接地的其他一些方面進(jìn)行管理����,包括控制可能導(dǎo)致性能降低的雜散接地和信號(hào)返回電壓。這些電壓可能是由于外部信號(hào)耦合�����、公共電流導(dǎo)致的,或者只是由于接地導(dǎo)線中的過(guò)度IR壓降導(dǎo)致的��。適當(dāng)?shù)夭季€����、布線的尺寸,以及差分信號(hào)處理和接地隔離技術(shù)�,使得我們能夠控制此類寄生電壓。

我們將要討論的一個(gè)重要主題是適用于模擬/數(shù)字混合信號(hào)環(huán)境的接地技術(shù)�����。事實(shí)上�����,高質(zhì)量接地這個(gè)問(wèn)題可以—也必然—影響到混合信號(hào)PCB設(shè)計(jì)的整個(gè)布局原則�����。

目前的信號(hào)處理系統(tǒng)一般需要混合信號(hào)器件���,例如模數(shù)轉(zhuǎn)換器(ADC)�、數(shù)模轉(zhuǎn)換器(DAC)和快速數(shù)字信號(hào)處理器(DSP)。由于需要處理寬動(dòng)態(tài)范圍的模擬信號(hào)�,因此必須使用高性能ADC和DAC。在惡劣的數(shù)字環(huán)境內(nèi)���,能否保持寬動(dòng)態(tài)范圍和低噪聲與采用良好的高速電路設(shè)計(jì)技術(shù)密切相關(guān)�����,包括適當(dāng)?shù)男盘?hào)布線�����、去耦和接地。

過(guò)去��,一般認(rèn)為"高精度����、低速"電路與所謂的"高速"電路有所不同。對(duì)于ADC和DAC����,采樣(或更新)頻率一般用作區(qū)分速度標(biāo)準(zhǔn)。不過(guò),以下兩個(gè)示例顯示�,實(shí)際操作中,目前大多數(shù)信號(hào)處理IC真正實(shí)現(xiàn)了"高速"�����,因此必須作為此類器件來(lái)對(duì)待��,才能保持高性能����。DSP、ADC和DAC均是如此����。

所有適合信號(hào)處理應(yīng)用的采樣ADC(內(nèi)置采樣保持電路的ADC)均采用具有快速上升和下降時(shí)間(一般為數(shù)納秒)的高速時(shí)鐘工作,即使呑吐量看似較低也必須視為高速器件����。例如,中速12位逐次逼近型(SAR) ADC可采用10 MHz內(nèi)部時(shí)鐘工作�����,而采樣速率僅為500 kSPS��。

Σ-Δ型ADC具有高過(guò)采樣比,因此還需要高速時(shí)鐘�����。即使是高分辨率的所謂"低頻"工業(yè)測(cè)量ADC(例如AD77xx-系列)吞吐速率達(dá)到10 Hz至7.5 kHz����,也采用5 MHz或更高時(shí)鐘頻率工作,并且提供高達(dá)24位的分辨率�。

更復(fù)雜的是,混合信號(hào)IC具有模擬和數(shù)字兩種端口�����,因此如何使用適當(dāng)?shù)慕拥丶夹g(shù)就顯示更加錯(cuò)綜復(fù)雜����。此外���,某些混合信號(hào)IC具有相對(duì)較低的數(shù)字電流���,而另一些具有高數(shù)字電流。很多情況下���,這兩種類型的IC需要不同的處理����,以實(shí)現(xiàn)最佳接地。

數(shù)字和模擬設(shè)計(jì)工程師傾向于從不同角度考察混合信號(hào)器件��,本文旨在說(shuō)明適用于大多數(shù)混合信號(hào)器件的一般接地原則�,而不必了解內(nèi)部電路的具體細(xì)節(jié)。

通過(guò)以上內(nèi)容��,顯然接地問(wèn)題沒(méi)有一本快速手冊(cè)����。遺憾的是,我們并不能提供可以保證接地成功的技術(shù)列表���。我們只能說(shuō)忽視一些事情�,可能會(huì)導(dǎo)致一些問(wèn)題�。在某一個(gè)頻率范圍內(nèi)行之有效的方法,在另一個(gè)頻率范圍內(nèi)可能行不通�。另外還有一些相互沖突的要求。處理接地問(wèn)題的關(guān)鍵在于理解電流的流動(dòng)方式�。

星型接地

"星型"接地的理論基礎(chǔ)是電路中總有一個(gè)點(diǎn)是所有電壓的參考點(diǎn),稱為"星型接地"點(diǎn)�。我們可以通過(guò)一個(gè)形象的比喻更好地加以理解—多條導(dǎo)線從一個(gè)共同接地點(diǎn)呈輻射狀擴(kuò)展���,類似一顆星。星型點(diǎn)并不一定在外表上類似一顆星—它可能是接地層上的一個(gè)點(diǎn)—但星型接地系統(tǒng)上的一個(gè)關(guān)鍵特性是:所有電壓都是相對(duì)于接地網(wǎng)上的某個(gè)特定點(diǎn)測(cè)量的�����,而不是相對(duì)于一個(gè)不確定的"地"(無(wú)論我們?cè)诤翁幏胖锰筋^)�。

雖然在理論上非常合理,但星型接地原理卻很難在實(shí)際中實(shí)施�����。舉例來(lái)說(shuō)�����,如果系統(tǒng)采用星型接地設(shè)計(jì)����,而且繪制的所有信號(hào)路徑都能使信號(hào)間的干擾最小并可盡量避免高阻抗信號(hào)或接地路徑的影響����,實(shí)施問(wèn)題便隨之而來(lái)。在電路圖中加入電源時(shí)����,電源就會(huì)增加不良的接地路徑�,或者流入現(xiàn)有接地路徑的電源電流相當(dāng)大和/或具有高噪聲��,從而破壞信號(hào)傳輸����。為電路的不同部分單獨(dú)提供電源(因而具有單獨(dú)的接地回路)通常可以避免這個(gè)問(wèn)題���。例如���,在混合信號(hào)應(yīng)用中,通常要將模擬電源和數(shù)字電源分開(kāi)�����,同時(shí)將在星型點(diǎn)處相連的模擬地和數(shù)字地分開(kāi)�����。

單獨(dú)的模擬地和數(shù)字地

事實(shí)上��,數(shù)字電路具有噪聲�����。飽和邏輯(例如TTL和CMOS)在開(kāi)關(guān)過(guò)程中會(huì)短暫地從電源吸入大電流。但由于邏輯級(jí)的抗擾度可達(dá)數(shù)百毫伏以上����,因而通常對(duì)電源去耦的要求不高。相反���,模擬電路非常容易受噪聲影響—包括在電源軌和接地軌上—因此��,為了防止數(shù)字噪聲影響模擬性能���,應(yīng)該把模擬電路和數(shù)字電路分開(kāi)。這種分離涉及到接地回路和電源軌的分開(kāi)���,對(duì)混合信號(hào)系統(tǒng)而言可能比較麻煩��。

然而�����,如果高精度混合信號(hào)系統(tǒng)要充分發(fā)揮性能�����,則必須具有單獨(dú)的模擬地和數(shù)字地以及單獨(dú)電源�����,這一點(diǎn)至關(guān)重要�����。事實(shí)上��,雖然有些模擬電路采用+5 V單電源供電運(yùn)行��,但并不意味著該電路可以與微處理器�、動(dòng)態(tài)RAM�、電扇或其他高電流設(shè)備共用相同+5 V高噪聲電源。模擬部分必須使用此類電源以最高性能運(yùn)行��,而不只是保持運(yùn)行��。這一差別必然要求我們對(duì)電源軌和接地接口給予高度注意�����。

請(qǐng)注意,系統(tǒng)中的模擬地和數(shù)字地必須在某個(gè)點(diǎn)相連�����,以便讓信號(hào)都參考相同的電位���。這個(gè)星點(diǎn)(也稱為模擬/數(shù)字公共點(diǎn))要精心選擇���,確保數(shù)字電流不會(huì)流入系統(tǒng)模擬部分的地。在電源處設(shè)置公共點(diǎn)通常比較便利��。

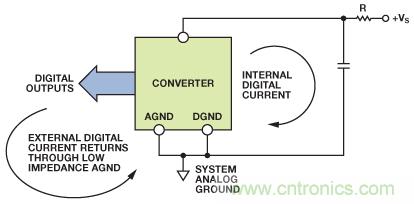

許多ADC和DAC都有單獨(dú)的"模擬地"(AGND)和"數(shù)字地"(DGND)引腳��。在設(shè)備數(shù)據(jù)手冊(cè)上���,通常建議用戶在器件封裝處將這些引腳連在一起�����。這點(diǎn)似乎與要求在電源處連接模擬地和數(shù)字地的建議相沖突���;如果系統(tǒng)具有多個(gè)轉(zhuǎn)換器,這點(diǎn)似乎與要求在單點(diǎn)處連接模擬地和數(shù)字地的建議相沖突��。

其實(shí)并不存在沖突。這些引腳的"模擬地"和"數(shù)字地"標(biāo)記是指引腳所連接到的轉(zhuǎn)換器內(nèi)部部分��,而不是引腳必須連接到的系統(tǒng)地����。對(duì)于ADC����,這兩個(gè)引腳通常應(yīng)該連在一起,然后連接到系統(tǒng)的模擬地���。由于轉(zhuǎn)換器的模擬部分無(wú)法耐受數(shù)字電流經(jīng)由焊線流至芯片時(shí)產(chǎn)生的壓降��,因此無(wú)法在IC封裝內(nèi)部將二者連接起來(lái)���。但它們可以在外部連在一起。

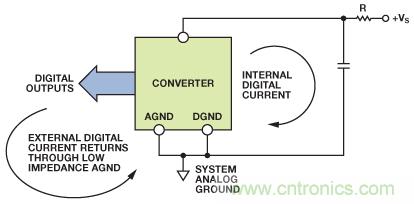

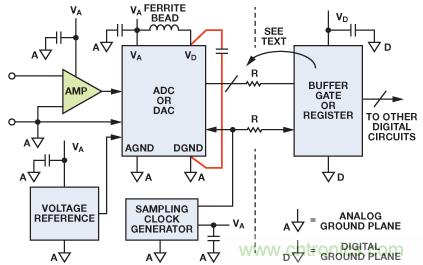

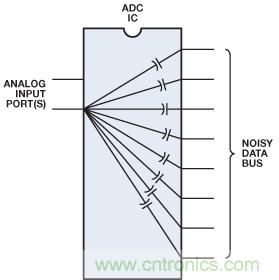

圖1顯示了ADC的接地連接這一概念����。這樣的引腳接法會(huì)在一定程度上降低轉(zhuǎn)換器的數(shù)字噪聲抗擾度,降幅等于系統(tǒng)數(shù)字地和模擬地之間的共模噪聲量�����。但是,由于數(shù)字噪聲抗擾度經(jīng)常在數(shù)百或數(shù)千毫伏水平�,因此一般不太可能有問(wèn)題。

模擬噪聲抗擾度只會(huì)因轉(zhuǎn)換器本身的外部數(shù)字電流流入模擬地而降低����。這些電流應(yīng)該保持很小,通過(guò)確保轉(zhuǎn)換器輸出沒(méi)有高負(fù)載����,可以最大程度地減小電流。實(shí)現(xiàn)這一目標(biāo)的好方法是在ADC輸出端使用低輸入電流緩沖器�����,例如CMOS緩沖器-寄存器IC�����。

如果轉(zhuǎn)換器的邏輯電源利用一個(gè)小電阻隔離�����,并且通過(guò)0.1 μF (100 nF)電容去耦到模擬地��,則轉(zhuǎn)換器的所有快速邊沿?cái)?shù)字電流都將通過(guò)該電容流回地�����,而不會(huì)出現(xiàn)在外部地電路中。如果保持低阻抗模擬地����,而能夠充分保證模擬性能,那么外部數(shù)字地電流所產(chǎn)生的額外噪聲基本上不會(huì)構(gòu)成問(wèn)題���。

接地層

接地層的使用與上文討論的星型接地系統(tǒng)相關(guān)。為了實(shí)施接地層����,雙面PCB(或多層PCB的一層)的一面由連續(xù)銅制造,而且用作地����。其理論基礎(chǔ)是大量金屬具有可能最低的電阻。由于使用大型扁平導(dǎo)體���,它也具有可能最低的電感��。因而����,它提供了最佳導(dǎo)電性能,包括最大程度地降低導(dǎo)電平面之間的雜散接地差異電壓�。

請(qǐng)注意,接地層概念還可以延伸�,包括 電壓層。電壓層提供類似于接地層的優(yōu)勢(shì)—極低阻抗的導(dǎo)體—但只用于一個(gè)(或多個(gè))系統(tǒng)電源電壓����。因此,系統(tǒng)可能具有多個(gè)電壓層以及接地層�。

雖然接地層可以解決很多地阻抗問(wèn)題,但它們并非靈丹妙藥�����。即使是一片連續(xù)的銅箔����,也會(huì)有殘留電阻和電感;在特定情況下���,這些就足以妨礙電路正常工作�。設(shè)計(jì)人員應(yīng)該注意不要在接地層注入很高電流�����,因?yàn)檫@樣可能產(chǎn)生壓降,從而干擾敏感電路��。

保持低阻抗大面積接地層對(duì)目前所有模擬電路都很重要��。接地層不僅用作去耦高頻電流(源于快速數(shù)字邏輯)的低阻抗返回路徑����,還能將EMI/RFI輻射降至最低。由于接地層的屏蔽作用�����,電路受外部EMI/RFI的影響也會(huì)降低���。

接地層還允許使用傳輸線路技術(shù)(微帶線或帶狀線)傳輸高速數(shù)字或模擬信號(hào),此類技術(shù)需要可控阻抗����。

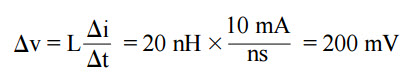

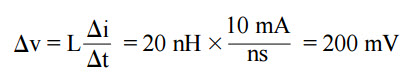

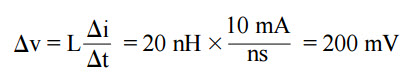

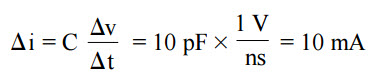

由于"總線(bus wire)"在大多數(shù)邏輯轉(zhuǎn)換等效頻率下具有阻抗,將其用作"地"完全不能接受���。例如��,#22標(biāo)準(zhǔn)導(dǎo)線具有約20 nH/in的電感�����。由邏輯信號(hào)產(chǎn)生的壓擺率為10 mA/ns的瞬態(tài)電流���,流經(jīng)1英寸該導(dǎo)線時(shí)將形成200 mV的無(wú)用壓降:

圖1. 數(shù)據(jù)轉(zhuǎn)換器的模擬地(AGND)和數(shù)字地(DGND)引腳應(yīng)返回到系統(tǒng)模擬地���。

如果轉(zhuǎn)換器的邏輯電源利用一個(gè)小電阻隔離,并且通過(guò)0.1 μF (100 nF)電容去耦到模擬地�����,則轉(zhuǎn)換器的所有快速邊沿?cái)?shù)字電流都將通過(guò)該電容流回地���,而不會(huì)出現(xiàn)在外部地電路中�����。如果保持低阻抗模擬地�����,而能夠充分保證模擬性能�,那么外部數(shù)字地電流所產(chǎn)生的額外噪聲基本上不會(huì)構(gòu)成問(wèn)題����。

接地層

接地層的使用與上文討論的星型接地系統(tǒng)相關(guān)�����。為了實(shí)施接地層����,雙面PCB(或多層PCB的一層)的一面由連續(xù)銅制造���,而且用作地����。其理論基礎(chǔ)是大量金屬具有可能最低的電阻����。由于使用大型扁平導(dǎo)體�����,它也具有可能最低的電感�����。因而,它提供了最佳導(dǎo)電性能���,包括最大程度地降低導(dǎo)電平面之間的雜散接地差異電壓���。

請(qǐng)注意,接地層概念還可以延伸�����,包括 電壓層�����。電壓層提供類似于接地層的優(yōu)勢(shì)—極低阻抗的導(dǎo)體—但只用于一個(gè)(或多個(gè))系統(tǒng)電源電壓���。因此����,系統(tǒng)可能具有多個(gè)電壓層以及接地層���。

雖然接地層可以解決很多地阻抗問(wèn)題����,但它們并非靈丹妙藥。即使是一片連續(xù)的銅箔�,也會(huì)有殘留電阻和電感;在特定情況下�����,這些就足以妨礙電路正常工作�����。設(shè)計(jì)人員應(yīng)該注意不要在接地層注入很高電流�����,因?yàn)檫@樣可能產(chǎn)生壓降�,從而干擾敏感電路。

保持低阻抗大面積接地層對(duì)目前所有模擬電路都很重要��。接地層不僅用作去耦高頻電流(源于快速數(shù)字邏輯)的低阻抗返回路徑���,還能將EMI/RFI輻射降至最低。由于接地層的屏蔽作用�����,電路受外部EMI/RFI的影響也會(huì)降低。

接地層還允許使用傳輸線路技術(shù)(微帶線或帶狀線)傳輸高速數(shù)字或模擬信號(hào)�,此類技術(shù)需要可控阻抗。

由于"總線(bus wire)"在大多數(shù)邏輯轉(zhuǎn)換等效頻率下具有阻抗����,將其用作"地"完全不能接受。例如���,#22標(biāo)準(zhǔn)導(dǎo)線具有約20 nH/in的電感��。由邏輯信號(hào)產(chǎn)生的壓擺率為10 mA/ns的瞬態(tài)電流�����,流經(jīng)1英寸該導(dǎo)線時(shí)將形成200 mV的無(wú)用壓降:

(1)

對(duì)于具有2 V峰峰值范圍的信號(hào)�����,此壓降會(huì)轉(zhuǎn)化為大約200 mV或10%的誤差(大約"3.5位精度")����。即使在全數(shù)字電路中����,該誤差也會(huì)大幅降低邏輯噪聲裕量���。

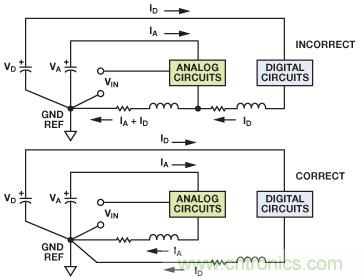

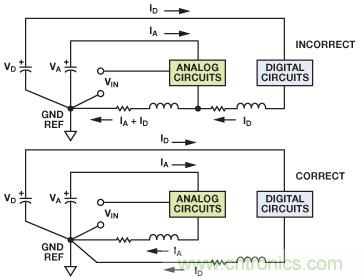

圖2顯示數(shù)字返回電流調(diào)制模擬返回電流的情況(頂圖)。接地返回導(dǎo)線電感和電阻由模擬和數(shù)字電路共享���,這會(huì)造成相互影響�,最終產(chǎn)生誤差����。一個(gè)可能的解決方案是讓數(shù)字返回電流路徑直接流向GND REF,如底圖所示�����。這顯示了"星型"或單點(diǎn)接地系統(tǒng)的基本概念�����。在包含多個(gè)高頻返回路徑的系統(tǒng)中很難實(shí)現(xiàn)真正的單點(diǎn)接地���。因?yàn)楦鞣祷仉娏鲗?dǎo)線的物理長(zhǎng)度將引入寄生電阻和電感����,所以獲得低阻抗高頻接地就很困難。實(shí)際操作中�����,電流回路必須由大面積接地層組成�,以便獲取高頻電流下的低阻抗�����。如果無(wú)低阻抗接地層��,則幾乎不可能避免上述共享阻抗����,特別是在高頻下。

所有集成電路接地引腳應(yīng)直接焊接到低阻抗接地層���,從而將串聯(lián)電感和電阻降至最低����。對(duì)于高速器件����,不推薦使用傳統(tǒng)IC插槽����。即使是"小尺寸"插槽�,額外電感和電容也可能引入無(wú)用的共享路徑,從而破壞器件性能�。如果插槽必須配合DIP封裝使用,例如在制作原型時(shí)����,個(gè)別"引腳插槽"或"籠式插座"是可以接受的。以上引腳插槽提供封蓋和無(wú)封蓋兩種版本���。由于使用彈簧加載金觸點(diǎn)��,確保了IC引腳具有良好的電氣和機(jī)械連接�����。不過(guò)��,反復(fù)插拔可能降低其性能����。

圖2. 流入模擬返回路徑的數(shù)字電流產(chǎn)生誤差電壓����。

應(yīng)使用低電感����、表面貼裝陶瓷電容����,將電源引腳直接去耦至接地層�。如果必須使用通孔式陶瓷電容,則它們的引腳長(zhǎng)度應(yīng)該小于1 mm��。陶瓷電容應(yīng)盡量靠近IC電源引腳��。噪聲過(guò)濾還可能需要鐵氧體磁珠���。

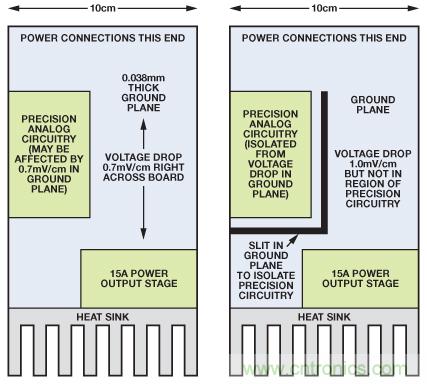

這樣的話�����,可以說(shuō)"地"越多越好嗎��?接地層能解決許多地阻抗問(wèn)題�����,但并不能全部解決��。即使是一片連續(xù)的銅箔��,也會(huì)有殘留電阻和電感���;在特定情況下����,這些就足以妨礙電路正常工作���。圖3說(shuō)明了這個(gè)問(wèn)題�����,并給出了解決方法�。

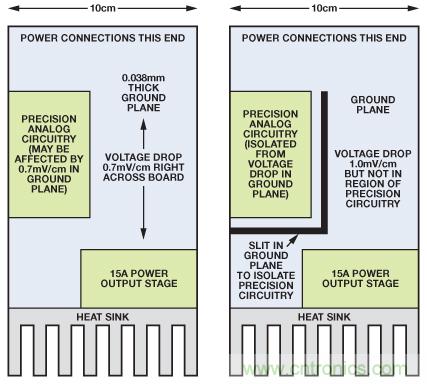

圖3. 割裂接地層可以改變電流流向���,從而提高精度��。

由于實(shí)際機(jī)械設(shè)計(jì)的原因���,電源輸入連接器在電路板的一端�����,而需要靠近散熱器的電源輸出部分則在另一端���。電路板具有100 mm寬的接地層,還有電流為15 A的功率放大器�����。如果接地層厚0.038 mm����,15 A的電流流過(guò)時(shí)會(huì)產(chǎn)生68 μV/mm的壓降��。對(duì)于任何共用該P(yáng)CB且以地為參考的精密模擬電路���,這種壓降都會(huì)引起嚴(yán)重問(wèn)題���。可以割裂接地層���,讓大電流不流入精密電路區(qū)域����,而迫使它環(huán)繞割裂位置流動(dòng)。這樣可以防止接地問(wèn)題(在這種情況下確實(shí)存在)��,不過(guò)該電流流過(guò)的接地層部分中電壓梯度會(huì)提高�����。

在多個(gè)接地層系統(tǒng)中�,請(qǐng)務(wù)必避免覆蓋接地層,特別是模擬層和數(shù)字層����。該問(wèn)題將導(dǎo)致從一個(gè)層(可能是數(shù)字地)到另一個(gè)層的容性耦合。要記住����,電容是由兩個(gè)導(dǎo)體(兩個(gè)接地層)組成的,中間用絕緣體(PC板材料)隔離�����。

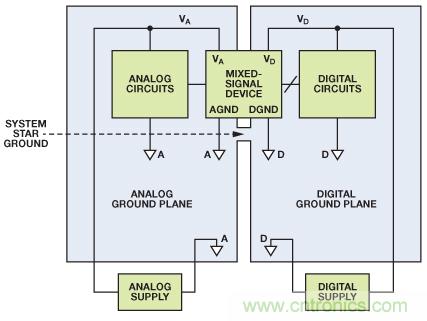

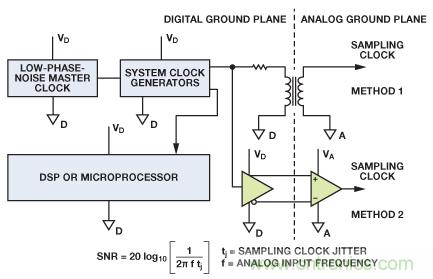

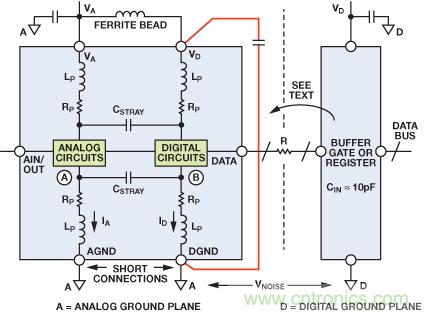

具有低數(shù)字電流的混合信號(hào)IC的接地和去耦

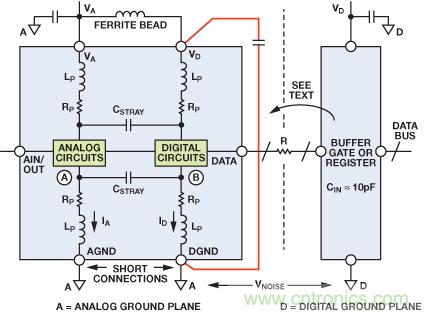

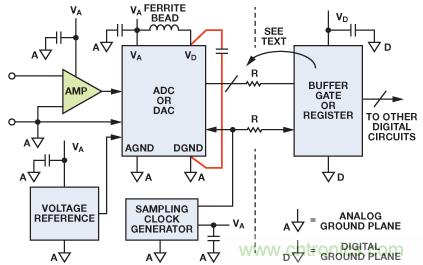

敏感的模擬元件��,例如放大器和基準(zhǔn)電壓源,必須參考和去耦至模擬接地層�����。具有低數(shù)字電流的ADC和DAC(和其他混合信號(hào)IC)一般應(yīng)視為模擬元件�,同樣接地并去耦至模擬接地層。乍看之下���,這一要求似乎有些矛盾�,因?yàn)檗D(zhuǎn)換器具有模擬和數(shù)字接口��,且通常有指定為模擬接地(AGND)和數(shù)字接地(DGND)的引腳����。圖4有助于解釋這一兩難問(wèn)題���。

圖4. 具有低內(nèi)部數(shù)字電流的混合信號(hào)IC的正確接地�����。

同時(shí)具有模擬和數(shù)字電路的IC(例如ADC或DAC)內(nèi)部�,接地通常保持獨(dú)立�����,以免將數(shù)字信號(hào)耦合至模擬電路內(nèi)。圖4顯示了一個(gè)簡(jiǎn)單的轉(zhuǎn)換器模型��。將芯片焊盤(pán)連接到封裝引腳難免產(chǎn)生線焊電感和電阻���,IC設(shè)計(jì)人員對(duì)此是無(wú)能為力的���,心中清楚即可??焖僮兓臄?shù)字電流在B點(diǎn)產(chǎn)生電壓,且必然會(huì)通過(guò)雜散電容CSTRAY耦合至模擬電路的A點(diǎn)�����。此外��,IC封裝的每對(duì)相鄰引腳間約有0.2 pF的雜散電容�,同樣無(wú)法避免!IC設(shè)計(jì)人員的任務(wù)是排除此影響讓芯片正常工作����。不過(guò),為了防止進(jìn)一步耦合��,AGND和DGND應(yīng)通過(guò)最短的引線在外部連在一起,并接到模擬接地層�����。DGND連接內(nèi)的任何額外阻抗將在B點(diǎn)產(chǎn)生更多數(shù)字噪聲��;繼而使更多數(shù)字噪聲通過(guò)雜散電容耦合至模擬電路��。請(qǐng)注意����,將DGND連接到數(shù)字接地層會(huì)在AGND和DGND引腳兩端施加 VNOISE ,帶來(lái)嚴(yán)重問(wèn)題����!

"DGND"名稱表示此引腳連接到IC的數(shù)字地,但并不意味著此引腳必須連接到系統(tǒng)的數(shù)字地����?�?梢愿鼫?zhǔn)確地將其稱為IC的內(nèi)部"數(shù)字回路"����。

這種安排確實(shí)可能給模擬接地層帶來(lái)少量數(shù)字噪聲,但這些電流非常小,只要確保轉(zhuǎn)換器輸出不會(huì)驅(qū)動(dòng)較大扇出(通常不會(huì)如此設(shè)計(jì))就能降至最低�����。將轉(zhuǎn)換器數(shù)字端口上的扇出降至最低(也意味著電流更低)���,還能讓轉(zhuǎn)換器邏輯轉(zhuǎn)換波形少受振鈴影響���,盡可能減少數(shù)字開(kāi)關(guān)電流,從而減少至轉(zhuǎn)換器模擬端口的耦合�。通過(guò)插入小型有損鐵氧體磁珠,如圖4所示�,邏輯電源引腳pin (VD) 可進(jìn)一步與模擬電源隔離。轉(zhuǎn)換器的內(nèi)部瞬態(tài)數(shù)字電流將在小環(huán)路內(nèi)流動(dòng)����,從VD 經(jīng)去耦電容到達(dá)DGND(此路徑用圖中紅線表示)。因此瞬態(tài)數(shù)字電流不會(huì)出現(xiàn)在外部模擬接地層上���,而是局限于環(huán)路內(nèi)�。VD引腳去耦電容應(yīng)盡可能靠近轉(zhuǎn)換器安裝���,以便將寄生電感降至最低����。去耦電容應(yīng)為低電感陶瓷型,通常介于0.01 μF (10 nF)和0.1 μF (100 nF)之間����。

再?gòu)?qiáng)調(diào)一次,沒(méi)有任何一種接地方案適用于所有應(yīng)用�。但是,通過(guò)了解各個(gè)選項(xiàng)和提前進(jìn)行規(guī)則���,可以最大程度地減少問(wèn)題����。

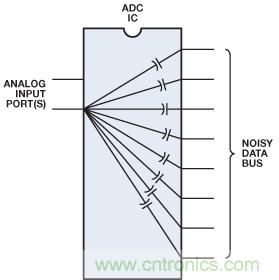

小心處理ADC數(shù)字輸出

將數(shù)據(jù)緩沖器放置在轉(zhuǎn)換器旁不失為好辦法�����,可將數(shù)字輸出與數(shù)據(jù)總線噪聲隔離開(kāi)(如圖4所示)���。數(shù)據(jù)緩沖器也有助于將轉(zhuǎn)換器數(shù)字輸出上的負(fù)載降至最低�,同時(shí)提供數(shù)字輸出與數(shù)據(jù)總線間的法拉第屏蔽(如圖5所示)�。雖然很多轉(zhuǎn)換器具有三態(tài)輸出/輸入��,但這些寄存器仍然在芯片上;它們使數(shù)據(jù)引腳信號(hào)能夠耦合到敏感區(qū)域���,因而隔離緩沖區(qū)依然是一種良好的設(shè)計(jì)方式����。某些情況下���,甚至需要在模擬接地層上緊靠轉(zhuǎn)換器輸出提供額外的數(shù)據(jù)緩沖器�,以提供更好的隔離����。

圖5. 在輸出端使用緩沖器/鎖存器的高速ADC 具有對(duì)數(shù)字?jǐn)?shù)據(jù)總線噪聲的增強(qiáng)抗擾度。

ADC輸出與緩沖寄存器輸入間的串聯(lián)電阻(圖4中標(biāo)示為"R")有助于將數(shù)字瞬態(tài)電流降至最低�,這些電流可能影響轉(zhuǎn)換器性能。電阻可將數(shù)字輸出驅(qū)動(dòng)器與緩沖寄存器輸入的電容隔離開(kāi)���。此外����,由串聯(lián)電阻和緩沖寄存器輸入電容構(gòu)成的RC網(wǎng)絡(luò)用作低通濾波器����,以減緩快速邊沿���。

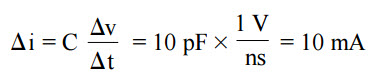

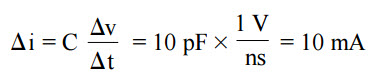

典型CMOS柵極與PCB走線和通孔結(jié)合在一起,將產(chǎn)生約10 pF的負(fù)載�����。如果無(wú)隔離電阻���,1 V/ns的邏輯輸出壓擺率將產(chǎn)生10 mA的動(dòng)態(tài)電流:

(2)

驅(qū)動(dòng)10 pF的寄存器輸入電容時(shí)����,500 Ω串聯(lián)電阻可將瞬態(tài)輸出電流降至最低�,并產(chǎn)生約11 ns的上升和下降時(shí)間:

(3)

圖6. 接地和去耦點(diǎn)。

由于TTL寄存器具有較高輸入電容��,可明顯增加動(dòng)態(tài)開(kāi)關(guān)電流����,因此應(yīng)避免使用

緩沖寄存器和其他數(shù)字電路應(yīng)接地并去耦至PC板的數(shù)字接地層。請(qǐng)注意�,模擬與數(shù)字接地層間的任何噪聲均可降低轉(zhuǎn)換器數(shù)字接口上的噪聲裕量。由于數(shù)字噪聲抗擾度在數(shù)百或數(shù)千毫伏水平�,因此一般不太可能有問(wèn)題。模擬接地層噪聲通常不高,但如果數(shù)字接地層上的噪聲(相對(duì)于模擬接地層)超過(guò)數(shù)百毫伏��,則應(yīng)采取措施減小數(shù)字接地層阻抗��,以將數(shù)字噪聲裕量保持在可接受的水平�����。任何情況下�����,兩個(gè)接地層之間的電壓不得超過(guò)300 mV����,否則IC可能受損����。

最好提供針對(duì)模擬電路和數(shù)字電路的獨(dú)立電源。模擬電源應(yīng)當(dāng)用于為轉(zhuǎn)換器供電����。如果轉(zhuǎn)換器具有指定的數(shù)字電源引腳(VD),應(yīng)采用獨(dú)立模擬電源供電���,或者如圖6所示進(jìn)行濾波���。所有轉(zhuǎn)換器電源引腳應(yīng)去耦至模擬接地層�����,所有邏輯電路電源引腳應(yīng)去耦至數(shù)字接地層�,如圖6所示���。如果數(shù)字電源相對(duì)安靜�,則可以使用它為模擬電路供電�,但要特別小心。

某些情況下����,不可能將VD連接到模擬電源。一些高速IC可能采用+5 V電源為其模擬電路供電�����,而采用+3.3 V或更小電源為數(shù)字接口供電�,以便與外部邏輯接口。這種情況下�,IC的+3.3 V引腳應(yīng)直接去耦至模擬接地層。另外建議將鐵氧體磁珠與電源走線串聯(lián),以便將引腳連接到+3.3 V數(shù)字邏輯電源���。

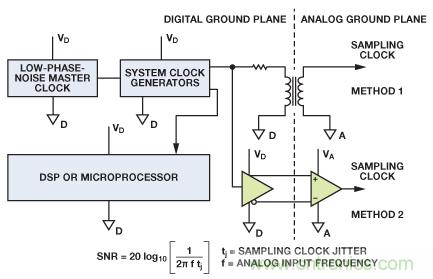

采樣時(shí)鐘產(chǎn)生電路應(yīng)與模擬電路同樣對(duì)待���,也接地并深度去耦至模擬接地層。采樣時(shí)鐘上的相位噪聲會(huì)降低系統(tǒng)信噪比(SNR)���;我們將稍后對(duì)此進(jìn)行討論。

采樣時(shí)鐘考量

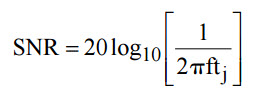

在高性能采樣數(shù)據(jù)系統(tǒng)中��,應(yīng)使用低相位噪聲晶體振蕩器產(chǎn)生ADC(或DAC)采樣時(shí)鐘���,因?yàn)椴蓸訒r(shí)鐘抖動(dòng)會(huì)調(diào)制模擬輸入/輸出信號(hào)��,并提高噪聲和失真底�����。采樣時(shí)鐘發(fā)生器應(yīng)與高噪聲數(shù)字電路隔離開(kāi)���,同時(shí)接地并去耦至模擬接地層,與處理運(yùn)算放大器和ADC一樣���。

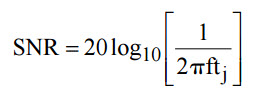

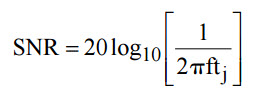

采樣時(shí)鐘抖動(dòng)對(duì)ADC信噪比(SNR)的影響可用以下公式4近似計(jì)算:

(4)

其中���,f為模擬輸入頻率�����,SNR為完美無(wú)限分辨率ADC的SNR���,此時(shí)唯一的噪聲源來(lái)自rms采樣時(shí)鐘抖動(dòng)tj。通過(guò)簡(jiǎn)單示例可知�,如果tj = 50 ps (rms),f = 100 kHz�����,則SNR = 90 dB�����,相當(dāng)于約15位的動(dòng)態(tài)范圍����。

應(yīng)注意,以上示例中的tj 實(shí)際上是外部時(shí)鐘抖動(dòng)和內(nèi)部ADC時(shí)鐘抖動(dòng)( 稱為孔徑抖動(dòng))的方和根(rss)值�����。不過(guò),在大多數(shù)高性能ADC中�,內(nèi)部孔徑抖動(dòng)與采樣時(shí)鐘上的抖動(dòng)相比可以忽略。

由于信噪比(SNR)降低主要是由于外部時(shí)鐘抖動(dòng)導(dǎo)致的�����,因而必須采取措施�,使采樣時(shí)鐘盡量無(wú)噪聲,僅具有可能最低的相位抖動(dòng)�。這就要求必須使用晶體振蕩器����。有多家制造商提供小型晶體振蕩器,可產(chǎn)生低抖動(dòng)(小于5 ps rms)的CMOS兼容輸出��。

理想情況下�����,采樣時(shí)鐘晶體振蕩器應(yīng)參考分離接地系統(tǒng)中的模擬接地層���。但是����,系統(tǒng)限制可能導(dǎo)致這一點(diǎn)無(wú)法實(shí)現(xiàn)。許多情況下���,采樣時(shí)鐘必須從數(shù)字接地層上產(chǎn)生的更高頻率��、多用途系統(tǒng)時(shí)鐘獲得��,接著必須從數(shù)字接地層上的原點(diǎn)傳遞至模擬接地層上的ADC�����。兩層之間的接地噪聲直接添加到時(shí)鐘信號(hào)����,并產(chǎn)生過(guò)度抖動(dòng)�����。抖動(dòng)可造成信噪比降低�����,還會(huì)產(chǎn)生干擾諧波�����。

圖7. 從數(shù)模接地層進(jìn)行采樣時(shí)鐘分配。

混合信號(hào)接地的困惑根源

大多數(shù)ADC����、DAC和其他混合信號(hào)器件數(shù)據(jù)手冊(cè)是針對(duì)單個(gè)PCB討論接地,通常是制造商自己的評(píng)估板�����。將這些原理應(yīng)用于多卡或多ADC/DAC系統(tǒng)時(shí)����,就會(huì)讓人感覺(jué)困惑茫然。通常建議將PCB接地層分為模擬層和數(shù)字層�,并將轉(zhuǎn)換器的AGND和DGND引腳連接在一起���,并且在同一點(diǎn)連接模擬接地層和數(shù)字接地層���,如圖8所示。這樣就基本在混合信號(hào)器件上產(chǎn)生了系統(tǒng)"星型"接地��。所有高噪聲數(shù)字電流通過(guò)數(shù)字電源流入數(shù)字接地層�����,再返回?cái)?shù)字電源;與電路板敏感的模擬部分隔離開(kāi)��。系統(tǒng)星型接地結(jié)構(gòu)出現(xiàn)在混合信號(hào)器件中模擬和數(shù)字接地層連接在一起的位置���。

該方法一般用于具有單個(gè)PCB和單個(gè)ADC/DAC的簡(jiǎn)單系統(tǒng)���,不適合多卡混合信號(hào)系統(tǒng)。在不同PCB(甚至在相同PCB上)上具有數(shù)個(gè)ADC或DAC的系統(tǒng)中��,模擬和數(shù)字接地層在多個(gè)點(diǎn)連接����,使得建立接地環(huán)路成為可能,而單點(diǎn)"星型"接地系統(tǒng)則不可能�����。鑒于以上原因�����,此接地方法不適用于多卡系統(tǒng)����,上述方法應(yīng)當(dāng)用于具有低數(shù)字電流的混合信號(hào)IC����。

圖8. 混合信號(hào)IC接地:?jiǎn)蝹€(gè)PCB(典型評(píng)估/測(cè)試板)��。

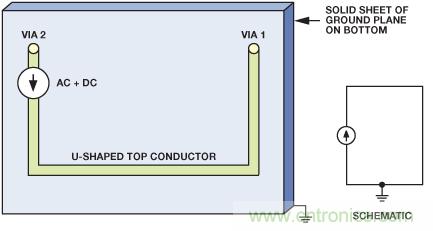

針對(duì)高頻工作的接地

一般提倡電源和信號(hào)電流最好通過(guò)"接地層"返回�,而且該層還可為轉(zhuǎn)換器、基準(zhǔn)電壓源和其它子電路提供參考節(jié)點(diǎn)���。但是�,即便廣泛使用接地層也不能保證交流電路具有高質(zhì)量接地參考����。

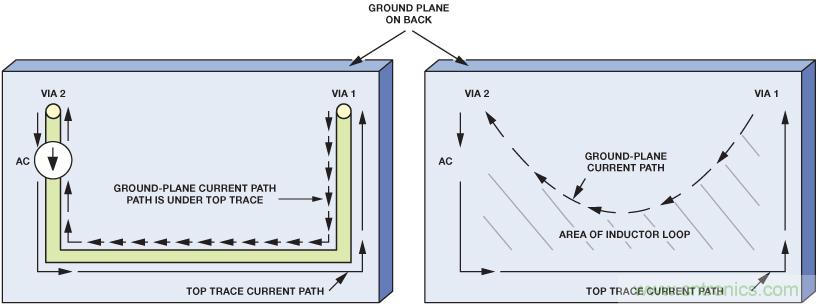

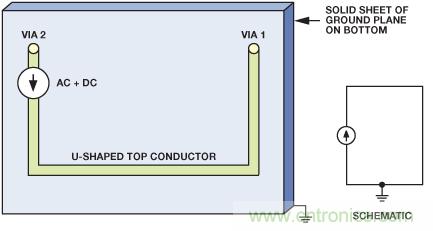

圖9所示的簡(jiǎn)單電路采用兩層印刷電路板制造,頂層上有一個(gè)交直流電流源�,其一端連到過(guò)孔1,另一端通過(guò)一條U形銅走線連到過(guò)孔2���。兩個(gè)過(guò)孔均穿過(guò)電路板并連到接地層。理想情況下��,頂端連接器以及過(guò)孔1和過(guò)孔2之間的接地回路中的阻抗為零���,電流源上的電壓為零���。

圖9. 電流源的原理圖和布局�����,PCB上布設(shè)U形走線����,通過(guò)接地層返回�。

這個(gè)簡(jiǎn)單原理圖很難顯示出內(nèi)在的微妙之處,但了解電流如何在接地層中從過(guò)孔1流到過(guò)孔2��,將有助于我們看清實(shí)際問(wèn)題所在�,并找到消除高頻布局接地噪聲的方法。

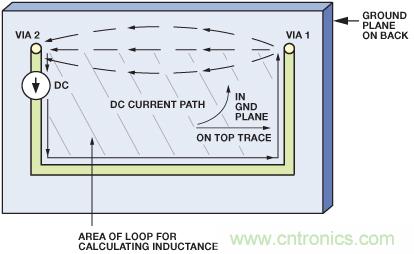

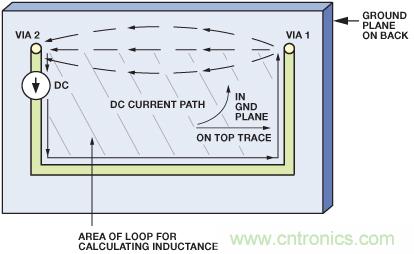

圖10. 圖9所示PCB的直流電流的流動(dòng)�。

圖10所示的直流電流的流動(dòng)方式,選取了接地層中從過(guò)孔1至過(guò)孔2的電阻最小的路徑�。雖然會(huì)發(fā)生一些電流擴(kuò)散,但基本上不會(huì)有電流實(shí)質(zhì)性偏離這條路徑��。相反��,交流電流則選取阻抗最小的路徑,而這要取決于電感����。

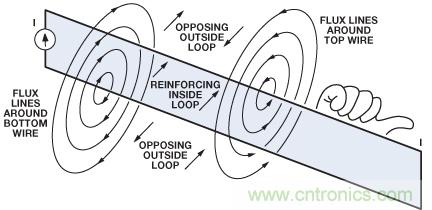

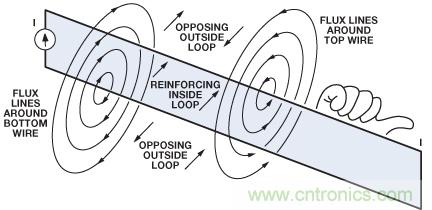

圖11. 磁力線和感性環(huán)路(右手法則)。

電感與電流環(huán)路的面積成比例�,二者之間的關(guān)系可以用圖11所示的右手法則和磁場(chǎng)來(lái)說(shuō)明。環(huán)路之內(nèi)�,沿著環(huán)路所有部分流動(dòng)的電流所產(chǎn)生的磁場(chǎng)相互增強(qiáng)。環(huán)路之外����,不同部分所產(chǎn)生的磁場(chǎng)相互削弱。因此�,磁場(chǎng)原則上被限制在環(huán)路以內(nèi)。環(huán)路越大則電感越大����,這意味著:對(duì)于給定的電流水平,它儲(chǔ)存的磁能(Li2)更多���,阻抗更高(XL = jωL)�,因而將在給定頻率產(chǎn)生更大電壓����。

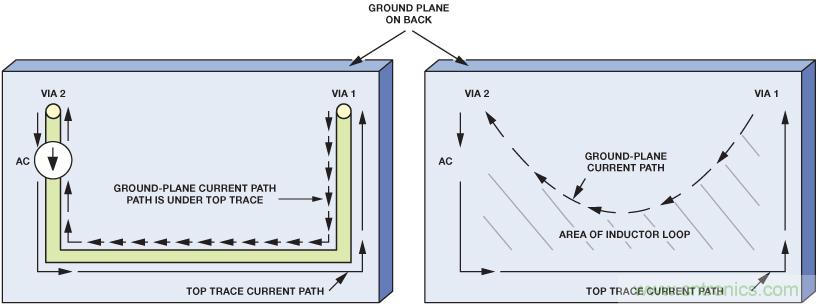

圖12. 接地層中不含電阻(左圖)和含電阻(右圖)的交流電流路徑。

電流將在接地層中選取哪一條路徑呢�?自然是阻抗最低的路徑?��?紤]U形表面引線和接地層所形成的環(huán)路����,并忽略電阻�����,則高頻交流電流將沿著阻抗最低��,即所圍面積最小的路徑流動(dòng)����。

在圖中所示的例子中,面積最小的環(huán)路顯然是由U形頂部走線與其正下方的接地層部分所形成的環(huán)路���。圖10顯示了直流電流路徑���,圖12則顯示了大多數(shù)交流電流在接地層中選取的路徑,它所圍成的面積最小�,位于U形頂部走線正下方。實(shí)際應(yīng)用中,接地層電阻會(huì)導(dǎo)致低中頻電流流向直接返回路徑與頂部導(dǎo)線正下方之間的某處�。不過(guò),即使頻率低至1 MHz或2 MHz�,返回路徑也是接近頂部走線的下方。

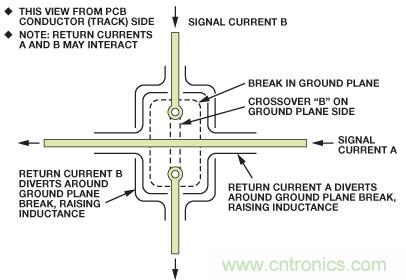

小心接地層割裂

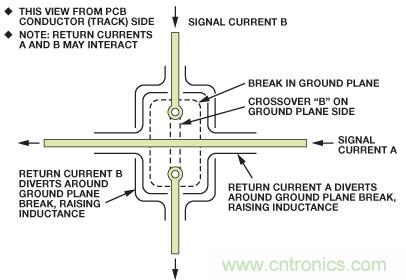

如果導(dǎo)線下方的接地層上有割裂��,接地層返回電流必須環(huán)繞裂縫流動(dòng)�����。這會(huì)導(dǎo)致電路電感增加���,而且電路也更容易受到外部場(chǎng)的影響�����。圖13顯示了這一情況���,其中的導(dǎo)線A和導(dǎo)線B必須相互穿過(guò)。

當(dāng)割裂是為了使兩根垂直導(dǎo)線交叉時(shí)�,如果通過(guò)飛線將第二根信號(hào)線跨接在第一根信號(hào)線和接地層上方,則效果更佳����。此時(shí)��,接地層用作兩個(gè)信號(hào)線之間的天然屏蔽體����,而由于集膚效應(yīng)�,兩路地返回電流會(huì)在接地層的上下表面各自流動(dòng),互不干擾����。

多層板能夠同時(shí)支持信號(hào)線交叉和連續(xù)接地層��,而無(wú)需考慮線鏈路問(wèn)題�。雖然多層板價(jià)格較高,而且不如簡(jiǎn)單的雙面電路板調(diào)試方便�����,但是屏蔽效果更好��,信號(hào)路由更佳���。相關(guān)原理仍然保持不變�,但布局布線選項(xiàng)更多。

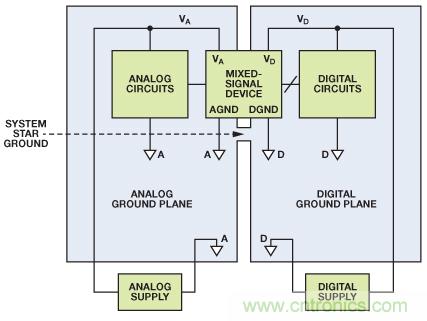

對(duì)于高性能混合信號(hào)電路而言��,使用至少具有一個(gè)連續(xù)接地層的雙面或多層PCB無(wú)疑是最成功的設(shè)計(jì)方法之一���。通常����,此類接地層的阻抗足夠低���,允許系統(tǒng)的模擬和數(shù)字部分共用一個(gè)接地層����。但是��,這一點(diǎn)能否實(shí)現(xiàn)��,要取決于系統(tǒng)中的分辨率和帶寬要求以及數(shù)字噪聲量����。

圖13. 接地層割裂導(dǎo)致電路電感增加,而且電路也更容易受到外部場(chǎng)的影響��。

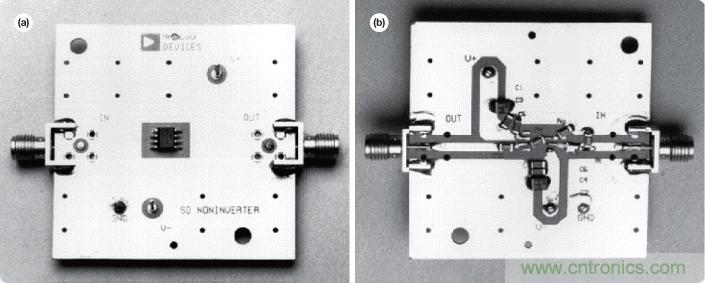

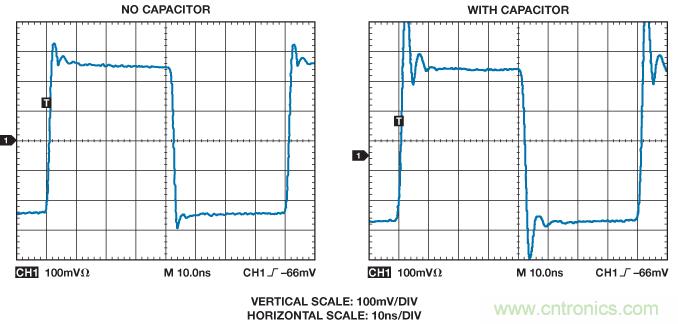

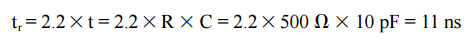

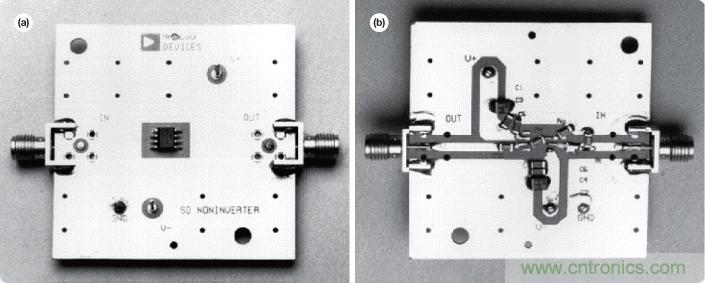

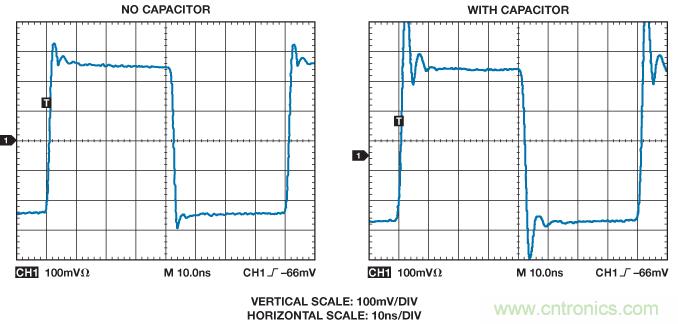

其他例子也可以說(shuō)明這一點(diǎn)。高頻電流反饋型放大器對(duì)其反相輸入周圍的電容非常敏感��。接地層旁的輸入走線可能具有能夠?qū)е聠?wèn)題的那一類電容�����。要記住��,電容是由兩個(gè)導(dǎo)體(走線和接地層)組成的�,中間用絕緣體(板和可能的阻焊膜)隔離���。在這一方面���,接地層應(yīng)與輸入引腳分隔開(kāi),如圖14所示���,它是AD8001高速電流反饋型放大器的評(píng)估板�。小電容對(duì)電流反饋型放大器的影響如圖15所示�。請(qǐng)注意輸出上的響鈴振蕩。

圖14. AD8001AR評(píng)估板—俯視圖(a)和仰視圖(b)���。

圖15. 10 pF反相輸入雜散電容對(duì) 放大器(AD8001)脈沖響應(yīng)的影響����。

接地總結(jié)

沒(méi)有任何一種接地方法能始終保證最佳性能。本文根據(jù)所考慮的特定混合信號(hào)器件特性提出了幾種可能的選項(xiàng)����。在實(shí)施初始PC板布局時(shí),提供盡可能多的選項(xiàng)會(huì)很有幫助���。

PC板必須至少有一層專用于接地層�����!初始電路板布局應(yīng)提供非重疊的模擬和數(shù)字接地層,如果需要��,應(yīng)在數(shù)個(gè)位置提供焊盤(pán)和過(guò)孔�����,以便安裝背對(duì)背肖特基二極管或鐵氧體磁珠��。此外,需要時(shí)可以使用跳線將模擬和數(shù)字接地層連接在一起���。

一般而言����,混合信號(hào)器件的AGND引腳應(yīng)始終連接到模擬接地層���。具有內(nèi)部鎖相環(huán)(PLL)的DSP是一個(gè)例外�,例如ADSP-21160 SHARC®處理器�。PLL的接地引腳是標(biāo)記的AGND�,但直接連接到DSP的數(shù)字接地層。

參考電路

Barrow, Jeff. “Avoiding Ground Problems in High Speed Circuits.” RF Design, July 1989.

Barrow, Jeff. “Reducing Ground Bounce in DC-to-DC Converters—Some Grounding Essentials.” Analog Dialogue. Vol. 41, No. 2, pp. 3-7, 2007.

Bleaney, B & B.I. Electricity and Magnetism. Oxford at the Clarendon Press, 1957: pp. 23, 24, and 52.

Brokaw, Paul. AN-202 Application Note. An IC Amplifier User’s Guide to Decoupling, Grounding and Making Things Go Right for a Change. Analog Devices, 2000.

Brokaw, Paul and Jeff Barrow. AN-345 Application Note. Grounding for Low- and High-Frequency Circuits. Analog Devices.

The Data Conversion Handbook. Edited by Walt Kester. Newnes, 2005. ISBN 0-7506-7841-0.

Johnson, Howard W. and Martin Graham. High-Speed Digital Design. PTR Prentice Hall, 1993. ISBN: 0133957241.

Kester, Walt. “A Grounding Philosophy for Mixed-Signal Systems.” Electronic Design Analog Applications Issue, June 23, 1997: pp. 29.

Kester, Walt and James Bryant. “Grounding in High Speed Systems.” High Speed Design Techniques. Analog Devices, 1996: Chapter 7, pp. 7-27.

Linear Circuit Design Handbook. Edited by Hank Zumbahlen. Newnes, February 2008. ISBN 978-0-7506-8703-4.

Montrose, Mark. EMC and the Printed Circuit Board. IEEE Press, 1999 (IEEE Order Number PC5756).

Morrison, Ralph. Grounding and Shielding Techniques. 4th Edition. John Wiley & Sons, Inc., 1998. ISBN: 0471245186.

Morrison, Ralph. Solving Interference Problems in Electronics. John Wiley & Sons, Inc., 1995.

Motchenbacher, C. D. and J. A. Connelly. Low Noise Electronic System Design. John Wiley & Sons, Inc., 1993.

Op Amp Applications Handbook. Edited by Walt Jung. Newnes, 2005. ISBN 0-7506-7844-5.

Ott, Henry W. Noise Reduction Techniques in Electronic Systems. 2nd Edition. John Wiley & Sons, Inc., 1988. ISBN: 0-471-85068-3.

Rempfer, William C. “Get All the Fast ADC Bits You Pay For.” Electronic Design. Special Analog Issue, June 24, 1996: pp. 44.

Rich, Alan. “Shielding and Guarding.” Analog Dialogue. Vol. 17, No. 1, pp. 8, 1983.

Sauerwald, Mark. “Keeping Analog Signals Pure in a Hostile Digital World.” Electronic Design. Special Analog Issue, June 24, 1996: pp. 57.

致謝

本文提供的材料由多名投稿人編輯�����,包括James Bryant��、Mike Byrne�����、Walt Jung����、Walt Kester�、Ray Stata以及ADI公司的工程設(shè)計(jì)人員�。

推薦閱讀:

(1)

(1)

(2)

(2)

(4)

(4)

(1)

(1)

(2)

(2)

(4)

(4)