【導(dǎo)讀】在本文中,將詳細(xì)研究這兩類隔離Σ-Δ調(diào)制器的輸出數(shù)據(jù)信號完整性。并通過簡單的電磁干擾(EMI)測試設(shè)置、對由這兩類Σ-Δ調(diào)制器的高頻時鐘信號產(chǎn)生的EMI進(jìn)行比較。

對輸出數(shù)據(jù)信號完整性和時鐘信號電磁干擾(EMI)的比較

隔離的Σ-Δ調(diào)制器長期以來被證明可以在嘈雜的工業(yè)電機(jī)應(yīng)用環(huán)境中提供非常高的精度和強(qiáng)勁的電流和電壓感測能力。有兩類隔離型Σ-Δ調(diào)制器:一種是在IC內(nèi)部產(chǎn)生時鐘信號;另一種是從外部時鐘源接收時鐘信號。 Σ-Δ調(diào)制器生成對應(yīng)于輸入模擬信號的輸出數(shù)字比特流數(shù)據(jù)。輸出數(shù)字?jǐn)?shù)據(jù)必須盡可能與時鐘信號同步。然后,微控制器以相同的時鐘信號頻率對該輸出數(shù)據(jù)進(jìn)行采樣,以進(jìn)一步濾波和抽取。

在本文中,將詳細(xì)研究這兩類隔離Σ-Δ調(diào)制器的輸出數(shù)據(jù)信號完整性。并通過簡單的電磁干擾(EMI)測試設(shè)置、對由這兩類Σ-Δ調(diào)制器的高頻時鐘信號產(chǎn)生的EMI進(jìn)行比較。

隔離型Σ-Δ調(diào)制器的簡化框圖

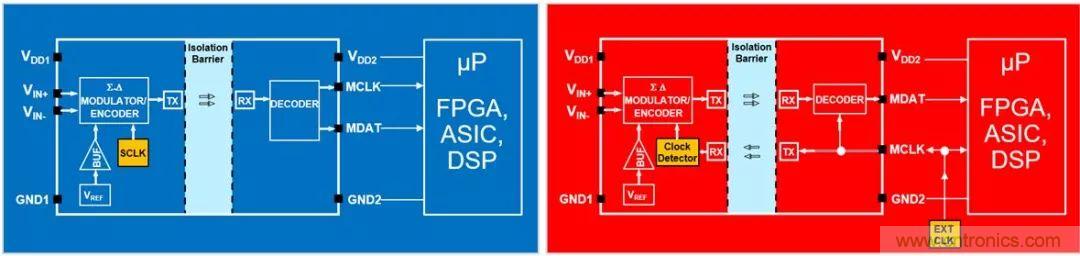

圖1左側(cè)的簡化框圖說明了典型的內(nèi)(部)時鐘隔離Σ-Δ調(diào)制器;右側(cè)是典型的外(部)時鐘隔離Σ-Δ調(diào)制器。對于內(nèi)時鐘型來說,抖動極低的時鐘源構(gòu)建在與Σ-Δ編碼器相同的芯片上。重新生成輸出MCLK,以允許輸出數(shù)據(jù)位流MDAT被脈送進(jìn)微控制器以進(jìn)行抽取和濾波。對于外時鐘型來說,外時鐘源為Σ-Δ調(diào)制器和微控制器提供時鐘信號。將在隔離柵的另一側(cè)檢測時鐘信號。檢測器必須能夠承受一定程度的時鐘抖動,并重構(gòu)時鐘信號,以實現(xiàn)Σ-Δ編碼器的正常功能。

圖1:左圖是內(nèi)時鐘隔離的Σ-Δ調(diào)制器簡化框圖;右圖是外時鐘隔離的Σ-Δ調(diào)制器的簡化框圖;兩者都連至微控制器。

輸出數(shù)據(jù)信號完整性

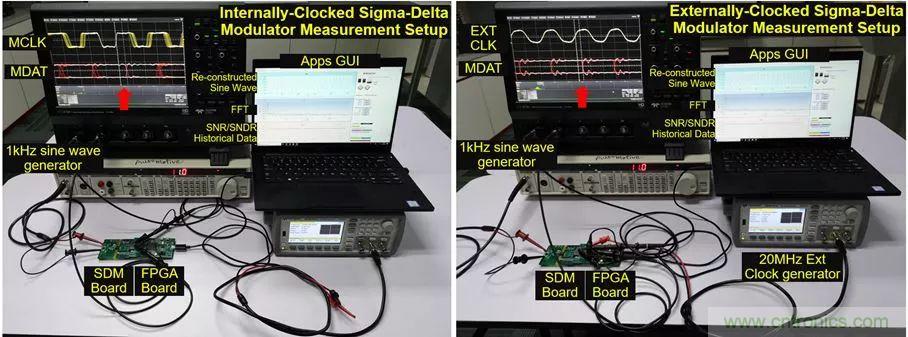

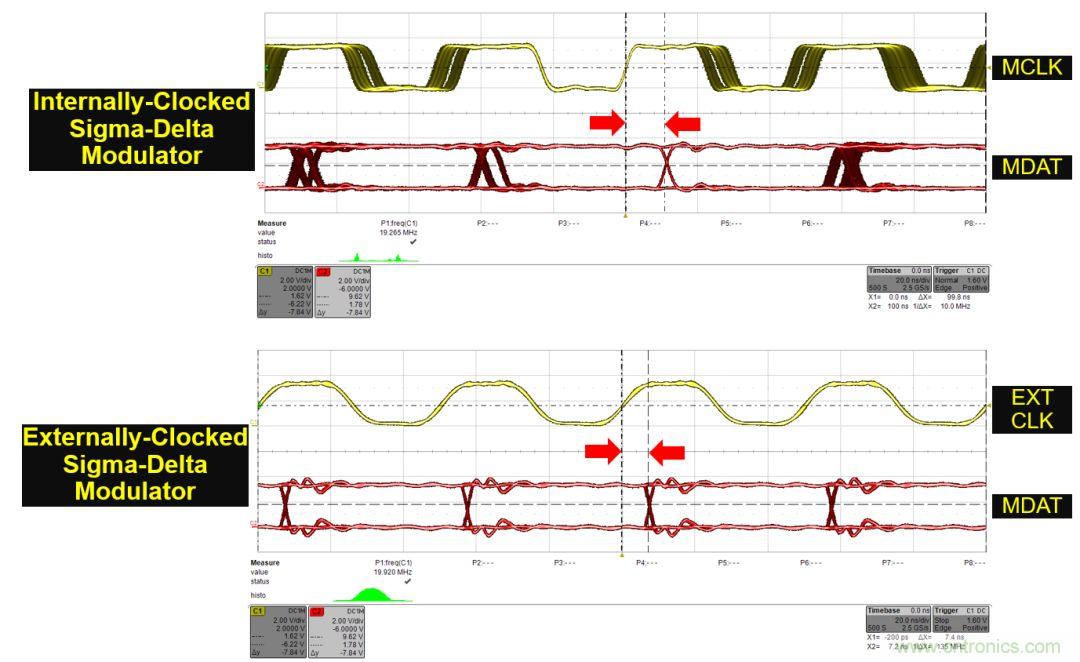

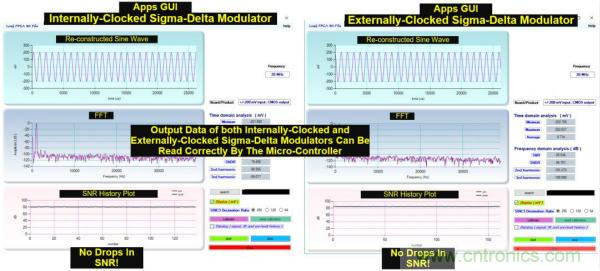

使用相同的微控制器(此例是FPGA),分別測量內(nèi)和外時鐘Σ-Δ調(diào)制器的信噪比(SNR)。這兩類Σ-Δ調(diào)制器的測量設(shè)置是相同的,只是外時鐘Σ-Δ調(diào)制器需要一個20MHz的外時鐘源提供時鐘信號。下面的圖2a和2b顯示了測量設(shè)置。將1kHz正弦波模擬電壓信號注入Σ-Δ調(diào)制器的輸入端,然后在FPGA處對相應(yīng)的數(shù)字輸出比特流數(shù)據(jù)進(jìn)行采樣,并經(jīng)過稱為抽取的濾波過程。筆記本電腦上顯示的應(yīng)用圖形用戶界面(GUI)顯示了重構(gòu)的正弦波、快速傅里葉變換(FFT),F(xiàn)FT用以計算信噪比(SNR)和SNR歷史圖與時間的對應(yīng)關(guān)系。如果FPGA未能正確采樣Σ-Δ輸出數(shù)據(jù)比特流,則將清楚地觀察到歷史圖上SNR的突然下降。

圖2a:顯示了具有相同F(xiàn)PGA板和應(yīng)用軟件的內(nèi)和外時鐘Σ-Δ調(diào)制器的測量設(shè)置。

圖2b:顯示了測量設(shè)置的簡化示意圖

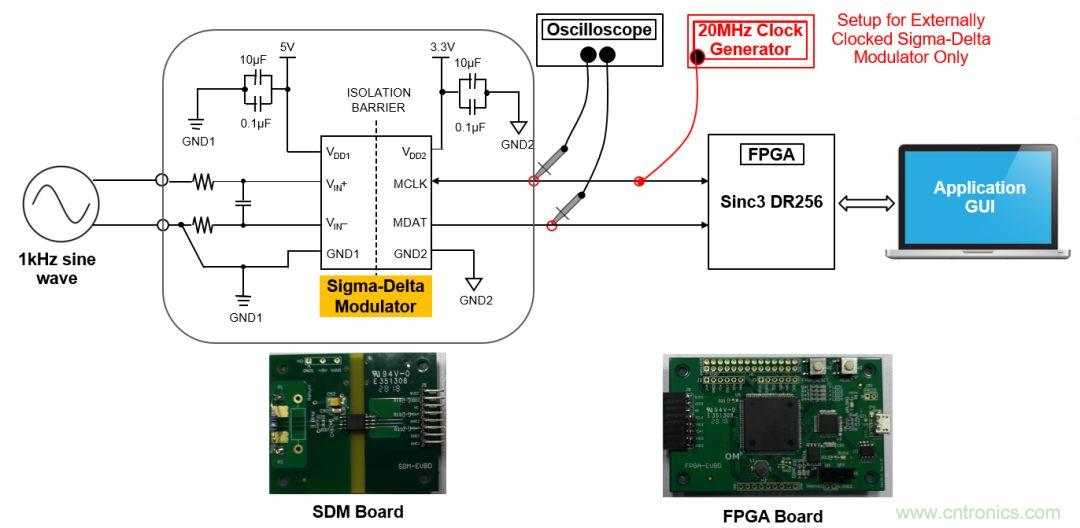

查看圖3中示波器捕獲的圖像,內(nèi)時鐘Σ-Δ調(diào)制器的輸出MCLK信號似乎是抖動的。但從輸出時鐘MCLK的上升沿到輸出數(shù)據(jù)MDAT的上升沿或下降沿的時間延遲,對每個時鐘周期看來都是相同的。同樣,從外時鐘到其輸出MDAT的時間延遲似乎也是穩(wěn)定的。這里可得出結(jié)論:對這兩類Σ-Δ調(diào)制器,MDAT在每個時鐘周期始終與MCLK同步。

圖3:顯示了示波器捕獲的兩類Σ-Δ調(diào)制器的MCLK和MDAT圖像

從圖4中所示的SNR歷史圖與時間的對比來看,對于兩類Σ-Δ調(diào)制器都沒有觀察到SNR的突然下降。換句話說,F(xiàn)PGA(微控制器)可正確讀取這兩類Σ-Δ調(diào)制器的輸出數(shù)據(jù)(MDAT)。

圖4:顯示了應(yīng)用GUI軟件中的測量結(jié)果

高頻時鐘信號產(chǎn)生的EMI

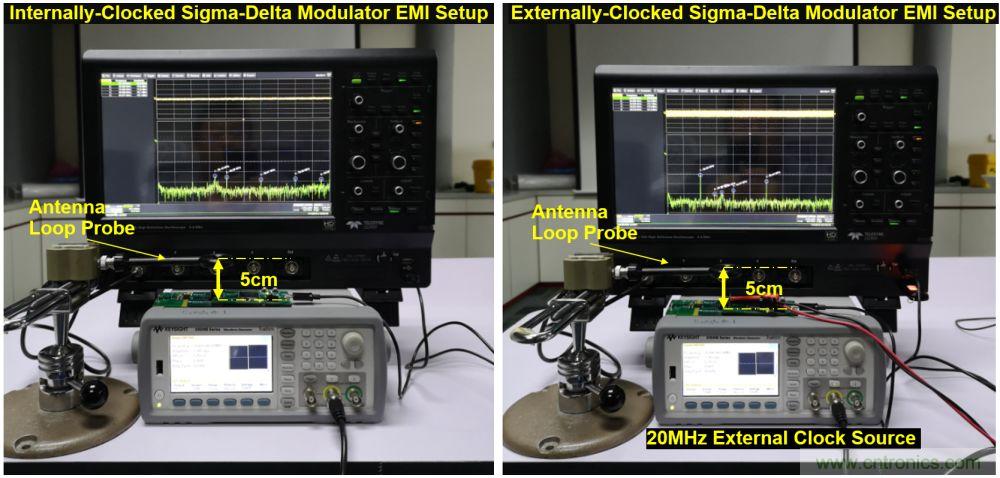

高頻時鐘信號是系統(tǒng)PCB板上EMI的主要來源之一。時鐘頻率越高、PCB走線越長,時鐘信號產(chǎn)生的EMI就越嚴(yán)重。內(nèi)時鐘Σ-Δ調(diào)制器的時鐘信號走線可以更短。一些內(nèi)時鐘的Σ-Δ調(diào)制器還結(jié)合了擴(kuò)頻技術(shù)來擴(kuò)展時鐘信號的頻率峰值,以有效降低EMI。為證明這點,設(shè)置了一種如圖5所示的簡單EMI測量方法,以分別測量內(nèi)和外時鐘Σ-Δ調(diào)制器的時鐘信號產(chǎn)生的EMI。將環(huán)形天線放置在Σ-Δ調(diào)制器評估板上方5cm處。示波器設(shè)置為將頻率從0Hz掃頻到100MHz。

圖5:顯示了該簡單的EMI測量設(shè)置,用于測量兩類Σ-Δ調(diào)制器的時鐘信號的EMI

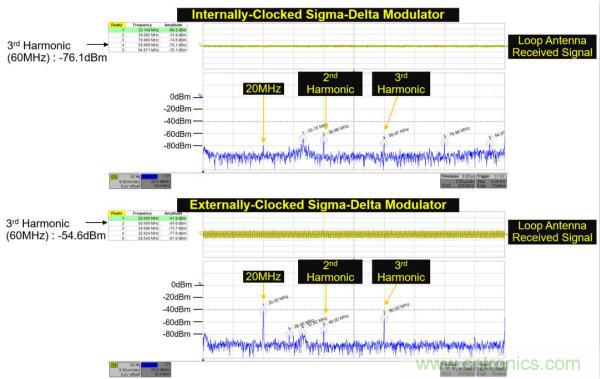

從圖6中示波器捕獲的圖像可以清楚看出,外時鐘源產(chǎn)生的EMI要高得多,在時鐘信號頻率及其諧波處達(dá)到峰值。例如,對于60MHz的三次諧波,外時鐘源產(chǎn)生的EMI比內(nèi)時鐘Σ-Δ調(diào)制器輸出時鐘信號的高20dB。

圖6:顯示了進(jìn)入外時鐘Σ-Δ調(diào)制器的時鐘信號產(chǎn)生的EMI要高得多,在時鐘信號頻率及其諧波處達(dá)到峰值

推薦閱讀: