【導(dǎo)讀】場效應(yīng)管的存在工程師們并不陌生,但是鰭式場效晶體管估計(jì)不是所有人都了解的。鰭式場效晶體管卻對集成電路物理設(shè)計(jì)及可測性設(shè)計(jì)流程具有重大影響。故了解鰭式場效晶體管是很必要的。本文將為大家詳解鰭式場效晶體管集成電路設(shè)計(jì)以及它的相關(guān)測試,話說做戲也要做全套的,希望對大家有用。

鰭式場效晶體管的出現(xiàn)對集成電路物理設(shè)計(jì)及可測性設(shè)計(jì)流程具有重大影響。鰭式場效晶體管的引進(jìn)意味著在集成電路設(shè)計(jì)制程中互補(bǔ)金屬氧化物(CMOS)晶體管必須被建模成三維(3D)的器件,這就包含了各種復(fù)雜性和不確定性。加州大學(xué)伯克利分校器件組的BSIM集團(tuán)開發(fā)出了一個(gè)模型,被稱作BSIM-CMG (common multi-gate)模型,來代表存在鰭式場效晶體管的電阻和電容。晶圓代工廠竭力提供精準(zhǔn)器件及寄生數(shù)據(jù),同時(shí)也致力于保留先前工藝所采用的使用模型。

寄生提取挑戰(zhàn)

然而,每個(gè)晶圓代工廠都會(huì)修改標(biāo)準(zhǔn)模型以使得更貼切地表現(xiàn)特定的架構(gòu)和工藝。此外,在這些先進(jìn)的工藝節(jié)點(diǎn)處,晶圓代工廠希望其通過參考場解算器建立的“黃金”模型與該領(lǐng)域設(shè)計(jì)人員使用提取工具得到的結(jié)果有更緊密的關(guān)聯(lián)。在28納米級節(jié)點(diǎn),晶圓代工廠希望商業(yè)提取工具精度介于其黃金模型的5%到10%之間。對于鰭式場效晶體管工藝,晶圓代工廠要求商業(yè)提取工具與黃金模型之間的平均精度誤差在2%以內(nèi),3倍離散標(biāo)準(zhǔn)偏差僅為6%-7%。

最具挑戰(zhàn)性的任務(wù)是計(jì)算鰭式場效晶體管與其周圍環(huán)境之間更復(fù)雜且無法估量的相互之間的寄生數(shù)據(jù),這需要涉及前段制程(FEOL)幾何結(jié)構(gòu)的精確3D建模。確保三維空間中的精度需要使用3D場解算器進(jìn)行提取。3D場解算器在先前用于制程特性而非設(shè)計(jì),因?yàn)槠溆?jì)算成本太高且速率太慢?,F(xiàn)在新一代的三維提取工具,比如Mentor的Calibre xACT,通過采用自我調(diào)整網(wǎng)格化技術(shù)加速計(jì)算的方法使其運(yùn)行速度比之前快了一個(gè)數(shù)量級。其還有可利用現(xiàn)代多CPU計(jì)算環(huán)境的高度可擴(kuò)容架構(gòu)。有了這些功能,提取工具可以輕松地在32 CPU機(jī)器上執(zhí)行場解算器計(jì)算解決方案,小至數(shù)個(gè)單元大至數(shù)百萬內(nèi)嵌晶體管的模塊。

在全芯片層次,我們需要考慮數(shù)十億晶體管設(shè)計(jì)以及幾千萬根連接導(dǎo)線,即使是快速場解算器也無法提出實(shí)用的周轉(zhuǎn)時(shí)間。解決方法是采用先進(jìn)的啟發(fā)式算法,對于復(fù)雜的結(jié)構(gòu)采用場解算器,對于一般的幾何圖形可采用基于表格的提取方法 (table-based)。這種方法是可行的,由于在布線網(wǎng)格中的電場模型類似于前制程節(jié)點(diǎn)所見的。在最理想的情況下,設(shè)計(jì)工程師所用的提取使用模型不會(huì)改變,因?yàn)樘崛」ぞ邥?huì)自動(dòng)在場解算器和表格方法之間移動(dòng)。

隨著雙重和三重光罩在從20納米級節(jié)點(diǎn)制造開始中扮演著越來越重要的作用,我們正經(jīng)歷著互連角點(diǎn)(interconnect corners)數(shù)量的飛躍。在28納米,5個(gè)互連角點(diǎn)是可能的,然而對于16納米級,我們預(yù)計(jì)需要11-15個(gè)角點(diǎn)。先進(jìn)的多角點(diǎn)分析計(jì)劃可以實(shí)現(xiàn)更高效的計(jì)算,減少每個(gè)額外角點(diǎn)所需的額外計(jì)算量。此外,我們可以并行處理角點(diǎn),以使每一個(gè)額外角點(diǎn)僅增加10%的整體周轉(zhuǎn)時(shí)間。這意味著15個(gè)角點(diǎn)只需要2.5倍的單個(gè)角點(diǎn)運(yùn)行時(shí)間。

[page]

測試挑戰(zhàn)

測試和失效分析是特別重要的,因?yàn)轹捠綀鲂Ьw管的關(guān)鍵尺寸首次比底層節(jié)點(diǎn)尺寸小得多。這使得提高的缺陷水平以及增加良率的挑戰(zhàn)日益受到關(guān)注。單元識(shí)別(Cell-Aware)的測試方法特別適合于解決這些問題,因?yàn)樗梢枣i定晶體管級的缺陷。相對來說,傳統(tǒng)的掃描測試模式只能識(shí)別單元之間互連件的缺陷。單元識(shí)別分析過程建立一個(gè)基于單元布局內(nèi)缺陷仿真行為的故障模型。結(jié)果能生產(chǎn)出更高質(zhì)量的圖形向量。當(dāng)采用單元識(shí)別方式自動(dòng)產(chǎn)生測試圖形向量(ATPG),硅驗(yàn)證結(jié)果表明從350納米級到鰭式場效晶體管級的技術(shù)節(jié)點(diǎn),明顯檢測出額外更多的缺陷,超出固定模式及過渡模式。

考慮具有三個(gè)鰭的多鰭式場效晶體管。最近的研究建議,這樣的晶體管應(yīng)考慮兩個(gè)缺陷類型:導(dǎo)致晶體管部分或全部擊穿的泄漏缺陷以及導(dǎo)致晶體管部分或完全關(guān)閉的驅(qū)動(dòng)強(qiáng)度缺陷。

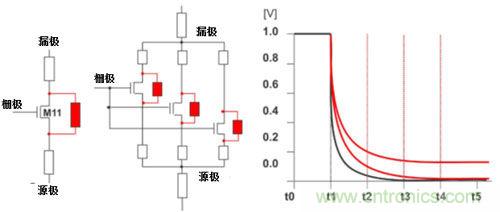

圖1:鰭式場效晶體管泄漏缺陷的測試

泄漏缺陷可以通過在每個(gè)晶體管的3鰭片兩端柵極(從漏極到源極)放置電阻來分析,如圖1所示。在單元識(shí)別分析過程中,模擬仿真(analog simulation)在一個(gè)給定單元庫對于所有鰭式場效晶體管的所有不同電阻值的電阻進(jìn)行。在晶體管在一定門閾值的情況下響應(yīng)延遲,對缺陷進(jìn)行建模。驅(qū)動(dòng)強(qiáng)度缺陷可以通過在漏極和每個(gè)柵極之間以及在源極和柵極之間放置電阻的方法來分析。至于泄漏測試,模擬仿真通過改變每個(gè)電阻的電阻值來進(jìn)行。每個(gè)鰭片的響應(yīng)時(shí)間差異用于決定是否需要進(jìn)行缺陷建模。其他的鰭式場效晶體管缺陷類型可以通過類似的方法來處理。

鰭式場效晶體管確實(shí)帶來了一些新的挑戰(zhàn),但電子設(shè)計(jì)自動(dòng)化工具供貨商和晶圓代工廠會(huì)盡全力以對集成電路設(shè)計(jì)流程影響最小的方式整合解決方案。

相關(guān)閱讀:

http://gpag.cn/power-art/80020398

http://gpag.cn/test-art/80019709