【導(dǎo)讀】為以16納米以下的制程節(jié)點(diǎn)生產(chǎn)IC設(shè)備,半導(dǎo)體制造商整合了許多新技術(shù),包括多重圖形、隔離層間距分割、3D邏輯與內(nèi)存結(jié)構(gòu)、新材料與復(fù)雜光罩。與這些創(chuàng)新技術(shù)相關(guān)的挑戰(zhàn)為半導(dǎo)體業(yè)界帶來了巨大的成本壓力。在這樣的環(huán)境中,高良率與快速提升良率在幫助半導(dǎo)體制造商保持盈利能力方面至關(guān)重要。

制程控制(process control)在過去30年,透過提供早期識(shí)別嚴(yán)重制程問題所需的檢測(cè)與度量技術(shù)幫助IC制造商提升良率。隨著IC設(shè)備設(shè)計(jì)節(jié)點(diǎn)隨時(shí)間收縮,制程控制系統(tǒng)透過實(shí)現(xiàn)支持檢測(cè)抑制良率與可靠性的缺陷及制程變化的創(chuàng)新技術(shù)跟上步伐。

例如KLA-Tencor的光學(xué)晶圓檢測(cè)系統(tǒng)在過去的30年已從使用鎢鹵素(tungsten-halogen)光源、現(xiàn)成的顯微物鏡和傳感器,發(fā)展成利用比太陽(yáng)更亮的雷射激發(fā)寬帶光源、與步進(jìn)機(jī)應(yīng)用相同復(fù)雜的光學(xué)組件,以及比數(shù)字相機(jī)快1,000倍的客制化傳感器。

目前的寬帶電漿光學(xué)圖形化晶圓檢測(cè)設(shè)備,能夠檢測(cè)到10納米的缺陷─那只比DNA鏈的直徑大四倍;要在12吋(300mm)晶圓片上的所有晶粒中檢測(cè)這些缺陷,困難度相當(dāng)于在像是美國(guó)加州那么大的區(qū)域范圍中,尋找散落距離可達(dá)數(shù)英哩的數(shù)百個(gè)硬幣─而且是在1小時(shí)之內(nèi)。

用于生產(chǎn)目前尖端設(shè)備的多種技術(shù)為制程控制帶來了挑戰(zhàn)。檢測(cè)與度量系統(tǒng)需能從較小的缺陷和制程/圖樣變化中擷取訊號(hào),這些擷取通常在具有高長(zhǎng)寬比特征的復(fù)雜 3D結(jié)構(gòu)上進(jìn)行。隨著新材料的使用和制程變化性的增加,訊號(hào)擷取需要在背景噪聲更強(qiáng)的環(huán)境中進(jìn)行。此外,隨著使用多重圖形和更多的制程步驟,檢測(cè)與度量工 具需要提高生產(chǎn)率,以便能執(zhí)行足夠用于檢測(cè)偏差的生產(chǎn)監(jiān)控。

例如,使用多重圖形技術(shù)生 產(chǎn)的FinFET晶體管需要使用借助于先進(jìn)檢測(cè)和度量系統(tǒng)的制程控制策略,這些系統(tǒng)整合了設(shè)計(jì)信息并能夠產(chǎn)生應(yīng)對(duì)較小的嚴(yán)重缺陷、3D結(jié)構(gòu)和窄制程容許范圍(process window)所需的靈敏度。此外,檢測(cè)與度量解決方案也必須提高生產(chǎn)率,以便經(jīng)濟(jì)有效地監(jiān)控使用多重圖形制造FinFET晶體管相關(guān)的、越來越多的制程步驟。

這些挑戰(zhàn)推動(dòng)了創(chuàng)新,催生能早期發(fā)現(xiàn)設(shè)計(jì)、圖形化或制程問題的獨(dú)特制程控制技術(shù)和解決方案;這類方案對(duì)于IC制造商至關(guān)重要,因?yàn)樗軌驅(qū)崿F(xiàn)今日的尖端技術(shù),以及未來能以更低風(fēng)險(xiǎn)與成本達(dá)到最大化提升良率與組件性能的技術(shù)。

制程控制的價(jià)值

做為制程控制核心的檢測(cè)與度量系統(tǒng)并不是用來制造IC設(shè)備,因?yàn)樗鼈儾粫?huì)添加/移除材料或者制作圖形;但制程控制對(duì)制造具備高良率的可靠組件至關(guān)重要,并非多余步驟。

透過查找缺陷和測(cè)量關(guān)鍵參數(shù),檢測(cè)與度量系統(tǒng)可監(jiān)控制造組件所需的數(shù)百個(gè)步驟。這些制程控制措施可幫助晶圓廠的工程師在出現(xiàn)偏差時(shí)確定制程問題并解決問題。制程控制從根本上與良率相關(guān)聯(lián),因?yàn)榫A廠不透過檢測(cè)與度量,幾乎無法查明影響良率的制程問題。

快速提高良率從而快速將產(chǎn)品推向市場(chǎng),對(duì)芯片制造商至關(guān)重要─良率提升有任何延誤都會(huì)影響營(yíng)收,并有可能影響用于研發(fā)的未來投資以及下一代產(chǎn)品的發(fā)表。透過實(shí)施諸如強(qiáng)大的制程控制策略等步驟,晶圓廠能縮短開發(fā)時(shí)間、加快生產(chǎn)速度和提高產(chǎn)品良率。

事實(shí)上,芯片制造商可從制程控制獲得的價(jià)值有多種形式,包括:強(qiáng)大的投資回報(bào)、更低的制造成本與風(fēng)險(xiǎn)、更高的營(yíng)收、更快的獲利速度、改善的產(chǎn)品周期、更高的利潤(rùn)以及業(yè)務(wù)連貫性。

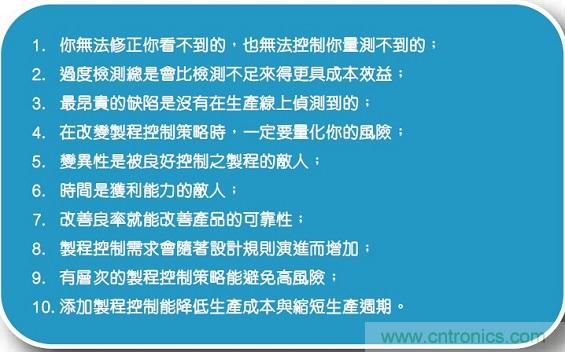

為讓讀者對(duì)制程控制價(jià)值有更進(jìn)一步了解,我們收集了“制程控制的十個(gè)基本事實(shí)”(圖1)。透過這十個(gè)事實(shí)來了解制程控制的基本特性,晶圓廠可以實(shí)施用于確定嚴(yán)重缺陷、查找偏差和減少變異來源的策略。

圖1 制程控制對(duì)半導(dǎo)體 IC 產(chǎn)業(yè)的十個(gè)基本事實(shí)。

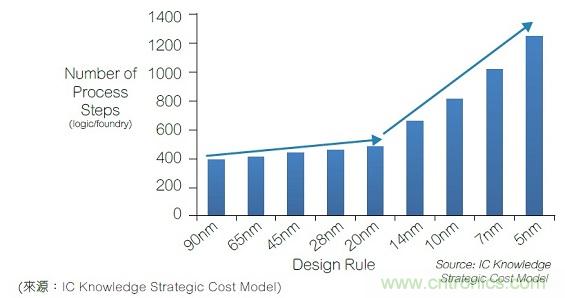

有鑒于先進(jìn)組件和制程整合日益升高的復(fù)雜度,晶圓廠在發(fā)展時(shí)必須考慮的最關(guān)鍵的事實(shí)為:制程控制需求會(huì)隨著設(shè)計(jì)規(guī)則演進(jìn)而增加。如圖 2所示,制程步驟數(shù)量從16/14納米節(jié)點(diǎn)開始急遽增加;隨著制程步驟的增加,所有步驟都必須為偏差、缺陷密度和變化性設(shè)定更高的標(biāo)準(zhǔn)。

圖2 制程步驟從16/14納米節(jié)點(diǎn)開始隨設(shè)計(jì)規(guī)則微縮而急遽增加。

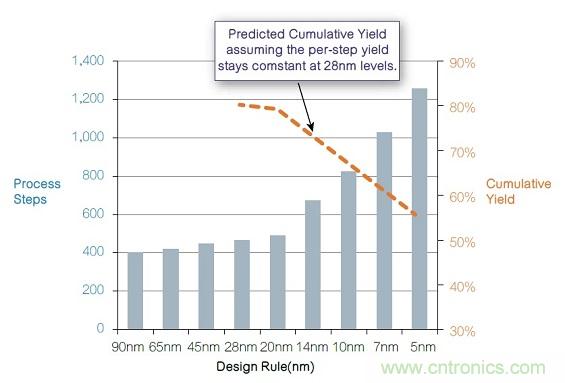

若每一個(gè)步驟的良率均保持在28納米節(jié)點(diǎn)的水平,那么每個(gè)較小設(shè)計(jì)節(jié)點(diǎn)的預(yù)測(cè)累積良率將降低(圖3)。考慮到這種良率損失的復(fù)合性質(zhì),晶圓廠須在每個(gè)獨(dú)立的制程步驟中保持更嚴(yán)格的控制和更低的缺陷密度。

圖3 隨著制程步驟的增加,如果每步驟良率均保持在28納米的水平,則先進(jìn)設(shè)計(jì)節(jié)點(diǎn)的預(yù)測(cè)累計(jì)良率將降低。

這驅(qū)動(dòng)對(duì)新制程控制策略的需要,這些策略不僅可檢測(cè)出嚴(yán)重影響良率的缺陷和微妙的制程變化,還可讓工程師增加檢測(cè)與度量樣本。此類制程控制能力支持對(duì)越來越多制程步驟的直接監(jiān)測(cè),以及快速檢測(cè)對(duì)晶圓制造成本具有顯著影響的偏差。

應(yīng)對(duì)未來制程控制挑戰(zhàn)的策略

在朝16納米以下設(shè)計(jì)節(jié)點(diǎn)進(jìn)軍時(shí),半導(dǎo)體制造商面臨摩爾定律(Moore''s Law)的諸多挑戰(zhàn)。在技術(shù)層面上,存在與整合新技術(shù)相關(guān)的諸多復(fù)雜因素(如多重圖形、3D結(jié)構(gòu)、新材料、復(fù)雜光罩、制程步驟的數(shù)量增加)。在經(jīng)濟(jì)層面 上,這些多種技術(shù)融合讓晶圓廠控制成本的壓力更大;晶體管成本與比例因子(scaling factor)、制造成本和良率有關(guān)。隨著制造、設(shè)計(jì)、開發(fā)和微影成本的增加,半導(dǎo)體制造商取得摩爾定律成本目標(biāo)的最佳解決方案為快速提升良率。

在嘗試快速提升良率時(shí),IC制造商必須克服圍繞設(shè)計(jì)強(qiáng)韌度與制程容許范圍的諸多問題。在設(shè)計(jì)層面上,工程師必須能夠發(fā)現(xiàn)和評(píng)估設(shè)計(jì)缺點(diǎn),以便推動(dòng)改進(jìn),從而確保設(shè)備設(shè)計(jì)與制造技術(shù)在生產(chǎn)中是穩(wěn)定的。

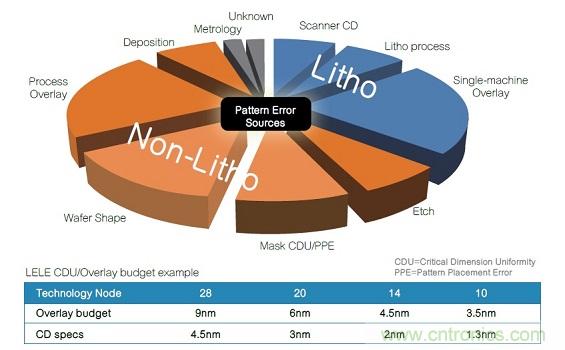

在 16納米以下的設(shè)計(jì)節(jié)點(diǎn)中,所需的圖形重迭預(yù)算(pattern overlay budget)為小于等于4.5納米,臨界尺寸規(guī)格為~2納米,制程容許范圍極窄。為推動(dòng)滿足這些嚴(yán)格的圖形化規(guī)格(圖4)所需的變更,工程師需要了解圖 形化錯(cuò)誤的整廠性來源(fab-wide sources)和變異性對(duì)制程容許范圍的影響。

圖4 對(duì)于先進(jìn)多重圖形技術(shù),圖形化錯(cuò)誤的來源是整廠性的─同時(shí)發(fā)生在微影單元的內(nèi)部與外部。為滿足極為嚴(yán)格的重迭與臨界尺寸規(guī)格,工程師必須設(shè)法減少制程變化的整廠性來源。

對(duì)于在成本目標(biāo)中應(yīng)對(duì)復(fù)雜技術(shù)挑戰(zhàn)的這一環(huán)境,制程控制至關(guān)重要。開發(fā)必要的制程控制解決方案具有挑戰(zhàn)─這需要巨大的創(chuàng)新和在半導(dǎo)體業(yè)界多個(gè)部門之間的密切 協(xié)作。這不僅對(duì)開發(fā)可提供先進(jìn)的檢測(cè)與度量系統(tǒng)效能的新技術(shù)很重要,也對(duì)追求朝向全面性制程控制解決方案的創(chuàng)新至關(guān)重要─這些策略將制程控制系統(tǒng)結(jié)合在一 起,從而使它們可以在晶圓廠中連同智能分析系統(tǒng)共同處理所產(chǎn)生的大量復(fù)雜資料。這些制程控制“系統(tǒng)中的系統(tǒng)”,可幫助晶圓廠透過快速設(shè)計(jì)驗(yàn)證和制程容許范圍發(fā)現(xiàn)、擴(kuò)展和控制快速提升良率。

缺陷發(fā)現(xiàn)的目標(biāo)為檢測(cè)和識(shí)別嚴(yán)重影響良率的缺陷,以突顯開發(fā)階段的設(shè)計(jì)問題和生產(chǎn)階段的制程漂移。發(fā)現(xiàn)系統(tǒng)(discovery system)憑借寬帶電漿光學(xué)缺陷檢測(cè)系統(tǒng)上的NanoPoin技術(shù)利用設(shè)計(jì)信息發(fā)現(xiàn)最嚴(yán)重影響良率的圖樣缺陷。

Surfscan SP5無圖形(unpatterned)晶圓檢測(cè)系統(tǒng)透過檢測(cè)微小的原片缺陷來幫助避免良率問題,這些缺陷可能扭曲先進(jìn)3D組件(如FinFET晶體管和 垂直NAND閃存)的后續(xù)薄膜與圖形結(jié)構(gòu)。最后,eDR-7110電子束審查與分類系統(tǒng)可以確定2920系列與Surfscan檢測(cè)器所檢測(cè)到的缺 陷。透過生成有關(guān)嚴(yán)重納米級(jí)缺陷的綜合信息,缺陷發(fā)現(xiàn)解決方案可幫助晶圓廠的工程師描述、優(yōu)化和監(jiān)控先進(jìn)制程,以便縮短上市時(shí)間。

5D 圖形化解決方案的目標(biāo)是幫助IC制造商在先進(jìn)組件上實(shí)現(xiàn)最佳的圖形化。借助目前復(fù)雜的多重圖形與隔離層間距分割技術(shù),圖形化錯(cuò)誤不再與微影單元有關(guān)。圖形 化錯(cuò)誤可能來自整廠性來源,如與掃描儀焦點(diǎn)錯(cuò)誤直接有關(guān)的CMP所導(dǎo)致的晶圓變形。5D解決方案利用多種類型的度量系統(tǒng)來確定和控制圖形化變異的整廠性來源,并透過智能分析系統(tǒng)來處理產(chǎn)生的數(shù)據(jù)。

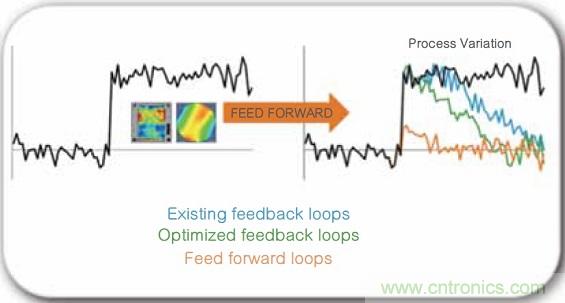

該系統(tǒng)解決方案的關(guān)鍵組成部分為回饋(feed back)和前饋(feed forward)度量資料能力(圖5)?;仞伝芈芬延糜诙鄠€(gè)設(shè)計(jì)節(jié)點(diǎn)。

圖 5 KLA-Tencor的5D圖形化控制解決方案透過實(shí)施多個(gè)數(shù)據(jù)回路來幫助優(yōu)化圖形化。現(xiàn)有的回饋回路(藍(lán))已存在于多個(gè)設(shè)計(jì)節(jié)點(diǎn)中,并對(duì)制程變化進(jìn)行檢測(cè)和補(bǔ)償。經(jīng)過優(yōu)化的新回饋回路(綠)可以更早地偵測(cè)制程變化。創(chuàng)新的前饋回路(橙)利用度量系統(tǒng)從源頭測(cè)量變更,然后將該數(shù)據(jù)前饋至后續(xù)制程步驟。

這種利用整廠性全面測(cè)量值與智能回饋組合以及前饋控制回路的5D解決方案,可幫助晶圓廠的工程師擴(kuò)大制程容許范圍并減輕這些窗口中的變化,最終獲得更好的圖形化結(jié)果。

這些綜合制程控制解決方案對(duì)IC業(yè)界的成功至關(guān)重要,它們透過使工程師可以更快和更經(jīng)濟(jì)有效地解決廣泛的制程問題來實(shí)現(xiàn)高良率并快速提高良率。在發(fā)展時(shí)必須維持創(chuàng)新與協(xié)作生態(tài)系統(tǒng),以確??梢蚤_發(fā)出能夠應(yīng)對(duì)IC制程與成本挑戰(zhàn)的新制程控制系統(tǒng)與解決方案。

【推薦閱讀】