【導(dǎo)讀】本應(yīng)用筆記對兩種模擬IC中常用的串行、數(shù)字接口(SPI™或3線、I²C或2線)進行了比較,每種接口在不同的設(shè)計中都表現(xiàn)出其優(yōu)點和缺點,具體取決于數(shù)據(jù)速率、可提供的設(shè)計空間以及噪聲環(huán)境等。本應(yīng)用筆記給出了兩種接口的區(qū)別,并舉例詳細說明了這些觀點。

引言

雖然現(xiàn)實世界中的信號都是模擬信號,但是現(xiàn)在越來越多的模擬IC采用數(shù)字接口進行通信。串行接口的數(shù)據(jù)通信介于主機(提供串行時鐘)和從機/外設(shè)之間。目前,大多數(shù)微控制器提供SPI (3線)和I²C (2線)接口,用于發(fā)送、接收數(shù)據(jù)。微處理器通過幾條總線控制周邊的設(shè)備,比如:模/數(shù)轉(zhuǎn)換器(ADC)、數(shù)/模轉(zhuǎn)換器(DAC)、智能電池、端口擴展、EEPROM以及溫度傳感器。與通過并口傳輸數(shù)據(jù)不同的是:串行接口通過2條、3條或4條數(shù)據(jù)/時鐘總線連續(xù)傳輸數(shù)據(jù)。雖然并行接口具有傳輸速度快的特點,但是串行接口占用較少的控制和數(shù)據(jù)線。

串行接口的基礎(chǔ)知識

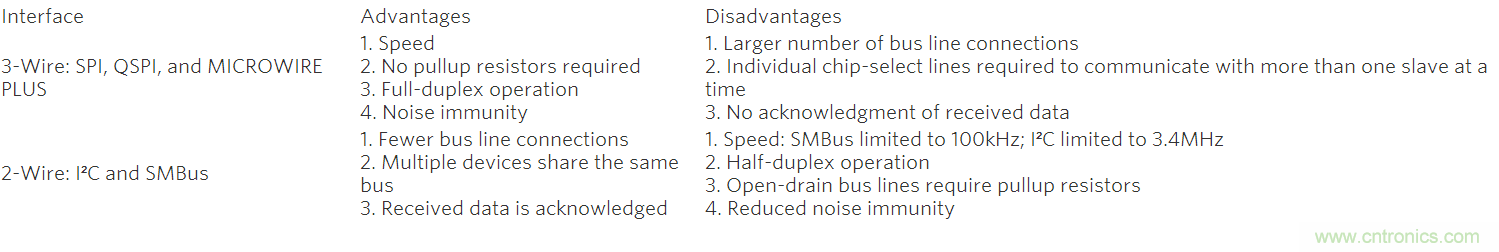

串行接口有三種:3線、2線和單線。本文主要討論3線和2線串行接口。串行外設(shè)接口(SPI)、隊列串行外設(shè)接口(QSPI™)和MICROWIRE™ (或MICROWIRE PLUS™)接口標(biāo)準(zhǔn)均采用3線接口。芯片間總線(I²C)和系統(tǒng)管理總線(SMBus™)均為2線接口。這些串行接口擁有各自的優(yōu)點和缺點,如表1所示。

3線接口

3線接口使用片選線(低電平有效CS或SS)、時鐘線(SCLK)和數(shù)據(jù)輸入/主機輸出線(DIN或MOSI)。3線接口有時也包括一條數(shù)據(jù)輸出/主機輸入線(DOUT或MISO),這時也叫做4線接口。為了敘述的簡便,本文將3線接口和4線接口統(tǒng)稱為3線接口。

3線接口可以以更高的時鐘頻率工作,并且不需要上拉電阻。SPI/QSPI和MICROWIRE接口都可以工作在全雙工模式(數(shù)據(jù)可以在同一時間發(fā)送和接收),一般在嘈雜環(huán)境下工作不成問題。3線接口是邊沿觸發(fā),不是電平觸發(fā),因此具有更強的抗干擾能力。

3線接口的主要缺點是它要為每一個從機提供一條低電平有效的CS線,除非將從機用菊鏈形式連接,如圖1所示(后續(xù)章節(jié)將詳細討論菊鏈方式)。另外一個缺點是3線接口沒有應(yīng)答機制去判斷數(shù)據(jù)的收發(fā)是否正確。從軟件設(shè)計看,在單主機/單從機應(yīng)用中,3線接口比2線接口簡單,效率更高。

圖1. 利用數(shù)據(jù)輸入、數(shù)據(jù)輸出、時鐘和片選信號進行通信的3線接口。

2線接口

2線接口包括一條數(shù)據(jù)線(SDA或SMBDATA)和一條時鐘線(SCL或SMBCLK)。2線接口的優(yōu)點是使用更少的連線,這一點對于結(jié)構(gòu)緊湊的設(shè)計尤為重要,比如:手機、光纖的應(yīng)用。因為2線接口為每個從機分配唯一的地址,所以可以在一條總線連接多個從機而不需要片選信號。2線接口在成功完成一次讀操作后會傳輸一個應(yīng)答位。因為2線接口只有一條數(shù)據(jù)線,所以它只能工作在半雙工模式(數(shù)據(jù)的讀寫不可以同時進行)。因為2線接口是電平觸發(fā),所以在嘈雜環(huán)境中如果發(fā)生數(shù)據(jù)位錯誤,可能造成問題。

表1. 3/2線接口優(yōu)缺點的對比

主機和從機經(jīng)由多條總線通過串行接口進行通訊。在寫周期,主機使用自己產(chǎn)生的時鐘和數(shù)據(jù)將數(shù)據(jù)傳至從機。在讀周期,從機傳輸數(shù)據(jù)至主機。

SPI、QSPI和MICROWIRE設(shè)計

由Motorola®制定的SPI接口已被很多流行的處理器和微控制器采用,比如MAXQ2000。SPI接口需要兩條控制線(低電平有效CS和SCLK)和兩條數(shù)據(jù)線(DIN/SDI和DOUT/SDO)。Motorola的SPI/QSPI標(biāo)準(zhǔn)稱DIN/SDI數(shù)據(jù)線為MOSI (主機出,從機入),DOUT/SDO數(shù)據(jù)線為MISO (主機入,從機出),CS線為SS (從機選擇)。為了敘述的清晰,我們基于從機說明3線接口的數(shù)據(jù)線。DIN是從機的數(shù)據(jù)輸入線,DOUT是從機的數(shù)據(jù)讀出線。本文采用低電平有效CS、SCLK、DIN和DOUT來定義3線接口中的各條線,Maxim外設(shè)使用了這些引腳名稱。

大多數(shù)的SPI接口有兩位配置位,時鐘極性(CPOL)和時鐘相位(CPHA)用于設(shè)定從機何時采集數(shù)據(jù)。CPOL決定SCLK為高時總線空閑(CPOL = 1)還是SCLK為低時總線空閑(CPOL = 0)。CPHA決定在SCLK的哪一個邊沿將數(shù)據(jù)移入、移出。當(dāng)CPOL = 0時,將CPHA設(shè)為0,表示在SCLK的上升沿將數(shù)據(jù)移入從機;將CPHA設(shè)為1,表示在SCLK的下降沿將數(shù)據(jù)移入從機。CPOL和CPHA的兩個狀態(tài)允許四種時鐘極性和相位的不同組合。每一種都與其它三種不兼容。為了實現(xiàn)主、從機間的通訊,主、從機的CPOL和CPHA必須有相同的設(shè)置。

在SPI接口的大多數(shù)應(yīng)用中,SPI接口一次傳送8位數(shù)據(jù)(一個字節(jié)),有一些微處理器一次傳送兩個或多個字節(jié)。例如,MAXQ2000微處理器可一次傳送8位或16位數(shù)據(jù)。當(dāng)CPOL = 0、CPHA = 0,低電平有效CS由高跳變?yōu)榈?,開始一個主機到從機的傳輸過程。在SCLK信號高低變化的八個周期內(nèi),低電平有效CS信號必須保持為低。DIN數(shù)據(jù)鎖定在SCLK信號的上升沿。在同樣的8位周期內(nèi),DOUT線上的從機輸出數(shù)據(jù)在SCLK的每個下降沿有效。圖2a給出了CPHA = 1時的詳細時序;圖2b給出了CPHA = 0時的詳細時序。

圖2a. 3線接口時序(CPHA = 1),CPHA = 1、CPOL = 1時,3線接口在時鐘的上升沿將數(shù)據(jù)移入外設(shè),在時鐘的下降沿將數(shù)據(jù)移出外設(shè)。

圖2b. 3線接口時序(CPHA = 0),CHPA = 0、CPOL = 1時,3線接口在時鐘的下降沿將數(shù)據(jù)移入外設(shè),在時鐘的上升沿將數(shù)據(jù)移出外設(shè)。

因為總線上的每一個IC需要專屬的片選線,所以低電平有效CS被用做每個從機的使能信號。如果一條總線上有四個從機,則需要四條片選線。如果從機的低電平有效CS為高電平(禁止),該從機就忽略SCLK線上的數(shù)據(jù),將DOUT置為高阻。

部分3線接口設(shè)備可以鏈接成菊鏈的方式,而不需要為每個從機提供低電平有效的CS線,菊鏈方式能夠用一條低電平有效的CS線和一條數(shù)據(jù)線控制多個串聯(lián)從機。在菊鏈結(jié)構(gòu)中3線接口必須包含DOUT線,如圖1所示,從機#1的DOUT連接到從機#2的DIN,如此反復(fù)。

SPI標(biāo)準(zhǔn)中沒有定義最大數(shù)據(jù)速率。外部設(shè)備定義了自己的最大數(shù)據(jù)速率,通常為MHz量級。微處理器可以適應(yīng)很寬范圍的SPI數(shù)據(jù)速率。在利用SPI接口進行通訊時,從機無法降低主機的數(shù)據(jù)速率或確定一個適當(dāng)?shù)乃俾省?/div>

QSPI標(biāo)準(zhǔn)和SPI標(biāo)準(zhǔn)非常相似。事實上,外設(shè)無法區(qū)分QSPI總線和SPI總線。與SPI標(biāo)準(zhǔn)中的主機不同,QSPI中的主機允許數(shù)據(jù)通過可編程的片選線傳輸數(shù)據(jù)。QSPI的主機甚至可以傳送長度在8位和16位之間的數(shù)據(jù),而SPI的主機只可以傳送8位的數(shù)據(jù)??梢耘渲肣SPI的設(shè)備去連續(xù)傳送長度超過16字節(jié)的數(shù)據(jù)(最大為256位)。這種傳輸完全由QSPI設(shè)備的配置來實現(xiàn),不需要MCU的操作。與SPI接口相似,QSPI接口也沒有規(guī)定最大數(shù)據(jù)速率。

由National Semiconductor公司制定的老的MICROWIRE標(biāo)準(zhǔn)和SPI標(biāo)準(zhǔn)非常相似。不同的是MICROWIRE標(biāo)準(zhǔn)的時鐘極性和時鐘相位是固定的(CPOL = 0和CPHA = 0)。DIN的數(shù)據(jù)讀取總是鎖定在SCLK的上升沿。DOUT的數(shù)據(jù)輸出總是在SCLK的下降沿。MICROWIRE標(biāo)準(zhǔn)沒有規(guī)定最大數(shù)據(jù)速率。

芯片間電路接口(I²C)

不同于全雙工的3線制接口,由Philips制定的I²C接口通過一條數(shù)據(jù)線(SDA)和一條時鐘線(SCL)實現(xiàn)半雙工通信。I²C接口定義了一個簡單的主/從雙向通信接口。在這個體系中,MCU決定自己為主機(寫模式)或為從機(接收模式)。每個從機具備專有、唯一的地址,使主機可以和多個從機通過一條總線進行通信,而不需要為每一個從機提供單獨的片選線。如圖3所示,從機的數(shù)目只受限于最大線上電容(400pF),I²C接口的機制基于7位或10位地址,7位的地址更為常見。在7位地址的機制中,總線上可以接127個不同的外設(shè)。SCL和SDA線為漏極開路結(jié)構(gòu),所以閑置時必須為高。當(dāng)電源電壓為3V時,連接一個1kΩ或更大阻值的上拉電阻;當(dāng)電源電壓為5V時,連接一個1.6kΩ或更大阻值的上拉電阻。

圖3. 利用數(shù)據(jù)輸入/輸出和時鐘信號進行通信的2線接口。

當(dāng)SCL為高,SDA從高變?yōu)榈?,即發(fā)出了一個開始命令,啟動I²C通信。圖4a所示,每個SCL時鐘傳輸一個數(shù)據(jù)位,傳輸一個字節(jié)至少需要9個數(shù)據(jù)位。一個寫周期包括8個數(shù)據(jù)位和一個應(yīng)答位(ACK)或者非應(yīng)答位(NACK)。如圖4b所示,當(dāng)數(shù)據(jù)在I²C總線上傳輸時,在SLK的上升沿寫入從機,在SLK的下降沿從機輸出。在SCL時鐘周期為高電平的時間內(nèi),SDA線的數(shù)據(jù)不可以改變。一次傳輸?shù)耐瓿杀仨毟S著一個中止或重新開始的命令,既SCL為高時,SDA由低變?yōu)楦摺.?dāng)總線空閑時,SDA和SCL都為高。

圖4a. 開始條件和停止條件,2線接口采用開始、重復(fù)開始和停止命令在主機和從機之間傳輸數(shù)據(jù)。

圖4b. I²C應(yīng)答位,應(yīng)答數(shù)據(jù)時,2線接口將SDA拉低。

I²C的寫周期起始于開始命令,隨后是7位從機地址和第8位用于標(biāo)識讀、寫操作。將第8位置低,表示寫操作;將第8位置高,表示讀操作。主機在第8個時鐘周期后釋放總線。如果從機應(yīng)答數(shù)據(jù)傳輸,則在第9個時鐘周期將SDA拉低。如果從機不應(yīng)答寫命令,則釋放SDA (該數(shù)據(jù)線通過上拉電阻置于高電平)。

隨后,主機寫入8位命令字節(jié),然后是第二個ACK/NACK位。接下來,主機寫入8位數(shù)據(jù)字節(jié)并跟隨第三個ACK/NACK位。數(shù)據(jù)字節(jié)和最后的應(yīng)答位完成一個讀/寫周期,更新外設(shè)輸出,圖5a是一個寫周期的詳細例子。

I²C讀周期起始于開始命令,隨后是需要寫入數(shù)據(jù)的從機地址、第8位置高,表示讀操作。在ACK/NACK之后,主機寫入命令字節(jié)訪問從機寄存器。在第二個ACK/NACK位后,主機重新寫入從機地址。在第三個ACK/NACK位后,從機控制總線,一次輸出8位數(shù)據(jù)到總線上。如圖5b所示,當(dāng)從與上次讀操作相同的從機寄存器讀取數(shù)據(jù)時,主機只需要在讀取從機數(shù)據(jù)之前寫入從機地址。

圖5. 2線接口一次傳輸8位數(shù)據(jù),圖5a是I²C寫周期的一個例子;圖5b是I²C讀周期的一個例子。

I²C接口支持低速(大于100kHz)、快速(大于400kHz)和高速(大于3.4MHz)三種數(shù)據(jù)速率。I²C接口的高低電平為CMOS邏輯電平(低電平為0.3x電源電壓以下,高電平為0.7x電源電壓以上)。

系統(tǒng)管理總線(SMBus)

Intel®制定了SMBus標(biāo)準(zhǔn)用于低速通信,SMBus 2線接口與I²C接口非常相似。SMBus也使用一條數(shù)據(jù)線(SMBDATA)和一條時鐘線(SMBCLK)進行通信。SMBCLK和SMBDATA也需要上拉電阻,3V供電時上拉電阻大于8.5kΩ,5V供電時上拉電阻大于14kΩ。SMBus工作電壓范圍在3V和5V之間,大于2.1V為高電平,低于0.8V為低電平。

I²C接口和SMBus接口的最主要區(qū)別是最高/最低時鐘速率,因為I²C總線為被動傳輸總線,不存在總線超時問題,速率可低至“靜止”。SMBus接口則存在總線超時問題。如果時鐘信號拉低之后的時間大于超時周期(最長為35ms)時,從機復(fù)位接口,認為發(fā)生總線超時。SMBus的超時周期限制了時鐘的最小速率為19kHz。為了保證正常通信,SMBCLK的速率必須介于10kHz至100kHz之間,而I²C接口的主機或從機則可根據(jù)傳輸數(shù)據(jù)的需要將時鐘保持在低電平。

外設(shè)舉例

微處理器經(jīng)常通過串行接口與外設(shè)通信,當(dāng)微處理器通過2線或3線接口訪問外設(shè)后,外設(shè)相應(yīng)地改變其模擬或數(shù)字輸出。例如,指使外設(shè)設(shè)置電池的充電的電流和電壓、用溫度傳感器控制風(fēng)扇、設(shè)置數(shù)模轉(zhuǎn)換器的模擬輸出等。

如圖6所示,通過2線接口連接微處理器和8位數(shù)/模轉(zhuǎn)換器(MAX5115)。因為這個DAC有四個地址選擇引腳,可以產(chǎn)生16個唯一的從機地址,因此可以在總線上并聯(lián)16個DAC,因為MAX6641有不同的從機地址,同樣的2線接口也可以設(shè)置SMBus溫度傳感器/風(fēng)扇控制器(MAX6641),風(fēng)扇控制器控制MOSFET的柵極,使其打開或關(guān)閉風(fēng)扇。

圖6. 由于微控制器采用的是I²C接口,與外設(shè)通信時,如DAC、溫度傳感器,總線只需要兩條連線。

3線接口需要單獨的片選線實現(xiàn)微處理器與多個并行從機之間的通信,更簡單的2線接口用一條時鐘線和一條數(shù)據(jù)線與總線上的每個設(shè)備通信??梢酝ㄟ^設(shè)定不同的從機地址在總線上掛接多個IC。大多數(shù)I²C接口外設(shè)具備地址選擇引腳,以實現(xiàn)從機地址的配置。外設(shè)可以使用的從地址數(shù)等于地址選擇引腳數(shù)的平方。例如,若外有兩個地址選擇引腳,它就可以配置四個不同的地址。

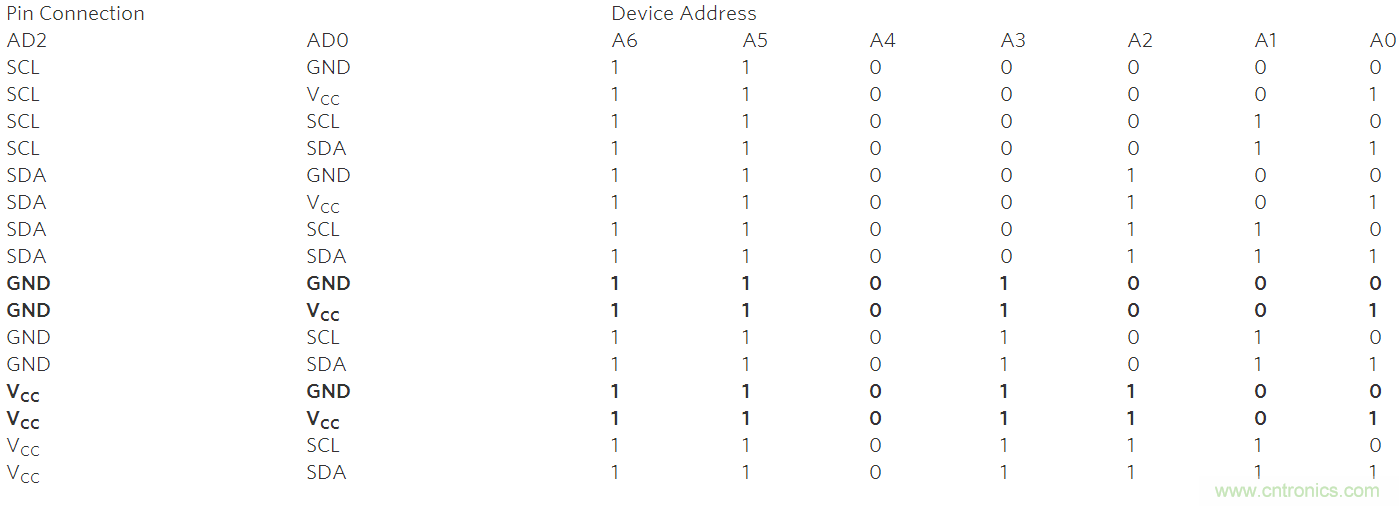

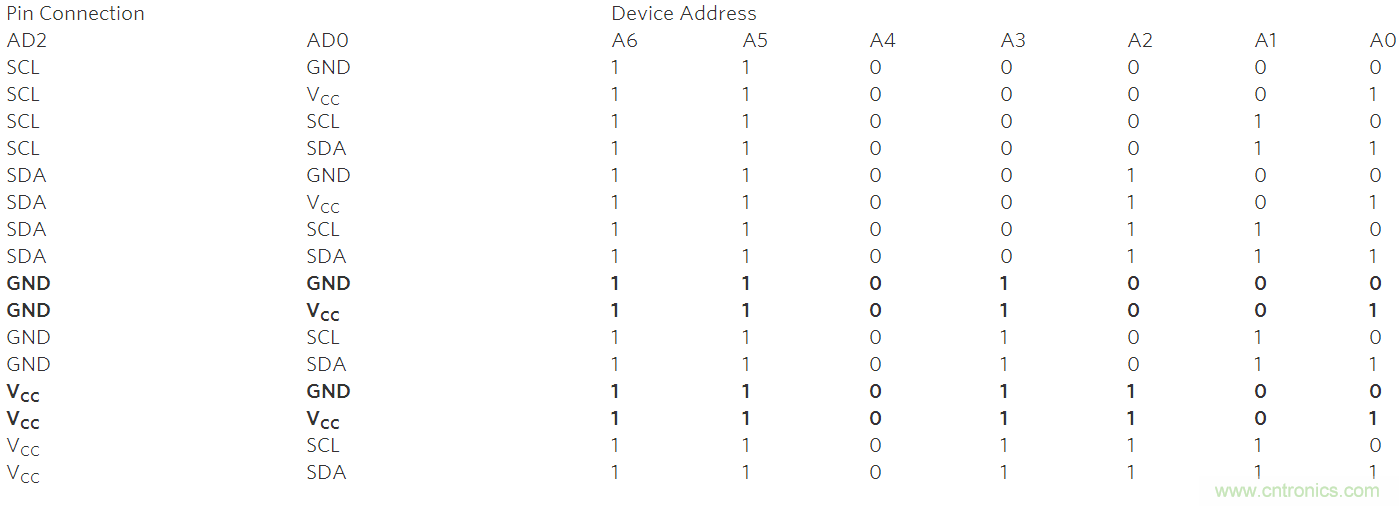

新一代設(shè)計以更少的地址選擇引腳提供更多的從地址。MAX7319是輸入/輸出擴展芯片,可以從兩個地址選擇引腳(AD2和AD0)擴展出16個從地址。這些引腳可以接GND、電源(VCC)、SDA或SCL。表2列出了這16個從地址的詳細信息,A6、A5、A4固定為110,A3至A0可以通過AD2、AD0設(shè)置。

表2. MAX7319僅利用2個地址線(AD2和AD0)即可編譯出16個不同地址

進一步改進

3線接口和2線接口有幾點不同的要求,每種接口都有其特殊優(yōu)勢。近期內(nèi)不可能用一種接口標(biāo)準(zhǔn)完全取代另一接口標(biāo)準(zhǔn)。具備I²C接口的器件發(fā)展較快,并開始融合一些SMBus接口的特點,支持諸如超時復(fù)位等功能,使接口可以根據(jù)需要關(guān)斷。新的I²C從機地址長達10位,而不僅僅是7位,這給用戶帶來更多的靈活性。

3線接口和2線接口將并存,但I²C接口似乎占有更大的市場份額,大部分微處理器支持2線接口。I²C接口的易用性及更少的連線使其增長量超過了SPI接口。

本文來源于Maxim。

推薦閱讀: