【導讀】眾所周知,德州儀器一直以來就是排名第一的模擬大廠,其電源控制器和模擬信號鏈產品占據較大的份額。因此,非常有必要說一說 TI 的 DCAP 系列控制器,它被廣泛地應用在計算機、服務器以及存儲等領域。

眾所周知,德州儀器一直以來就是排名第一的模擬大廠,其電源控制器和模擬信號鏈產品占據較大的份額。因此,非常有必要說一說 TI 的 DCAP 系列控制器,它被廣泛地應用在計算機、服務器以及存儲等領域。前面已經說過 DCAP 控制器也是 ACOT 原理的控制器,TI 把它稱為“Direct connection to the output CAPacitor”,縮寫為 DCAP。

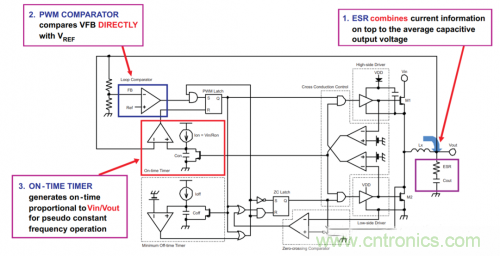

圖 42DCAP 控制器框圖

相信看過 TI 官網資料的朋友一定對這個 DCAP 控制器框圖很熟悉。它和我們之前搭建的 COT 控制器的模型基本一致,包含了恒定時間定時器(On-time Timer)、最小關斷時間定時器(Minimum Off-time Timer)、電流過零檢測(Zero-crossingDetection)、以及上下管的驅動。

輸出電壓通過簡單的分壓網絡做采樣得到含有 ESR 紋波的反饋信號,反饋信號 vfb 和參考電壓 vref 比較,當 vfb 低于 vref 時,比較器輸出拉高。此時,最小關斷定時器也需要準備好,在上一個開關周期中關斷階段,當 PWM latch Q 拉低時,最小關斷定時器才開始以恒定電流 Ioff 給 Coff 充電,當 Coff 電壓大于設定好的參考電壓時,最小關斷定時器的比較器輸出一定會拉高。接著往右看,這里多了一個或門,PWM latch Q 是拉低的,最小關斷定時器的輸出是拉高的,因此或門的輸出在上一個周期的關斷階段一定是高電平。這個高電平輸入到與門,它會一直等待 vfb 低于 vref,Loop 比較器拉高信號的到來。等與門的兩個輸入都為高電平之后,PWM latch 的 S 拉高,使得 PWMlatch Q 拉高,從而驅動上管的驅動拉高。

只不過在這里,PWM latch Q 的高電平信號之后接入了另一個與門,它也需要等待下管關斷信號結束,防止上下管的直通,也即是圖中的 cross conduction control。同樣地,下管的驅動信號做了一毛一樣的邏輯處理。

恒定導通定時器的控制和之前表述的 ACOT 一毛一樣,不多言。

值得注意的是,ZCD 過零檢測部分,與之前介紹的方式比較類似。通過在關斷階段采樣開關結點的電壓,當電壓逐漸增大變?yōu)檎妷簳r,比較器翻轉,關斷下管的驅動信號,從而進入 DCM 模式。想象一下,ZC latch 的 S 端什么時候會拉高呢?S 端接入了一個非門,在非門之前的信號就是最小關斷定時器的輸出和 PWM latch Q 輸出的或信號。所以,只有一種,PWM latch Q 和最小關斷定時器的比較器輸出,兩者都拉低。

實際上,PWM latch Q 控制著最小關斷定時器 Coff 電容電壓。Q 拉高,Coff 電壓被放電至零,最小關斷定時器的比較器輸出一定是低;Q 拉低,Coff 電壓被充電,未充到設定的參考電壓時,最小關斷定時器的比較器輸出是低,充到設定的參考電壓時,最小關斷定時器的比較器輸出為高。所以,只有在最小關斷定時器充電階段,才滿足上述兩者均拉低的要求。因此可以判定,ZC latch S 由 Q 拉低觸發(fā),這么做當然是為了 SW 降低到二極管鉗位電壓之后才開始采樣。筆者比較擔心的是,從 Q 信號到 SW 真正拉低至下管的體二極管鉗位電壓時,仍然有比較大的時間延遲。就有可能出現,Q 拉低觸發(fā) ZCD 檢測開始,而 SW 還處在從 Vin 下降的階段,從而引起 ZCD 信號誤動作。

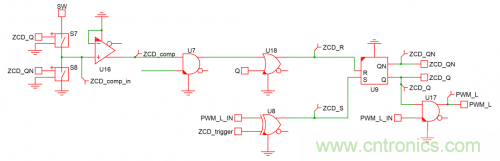

圖 43 part9 中的 ZCD 邏輯(為了方便表述,再貼一次)

細心的讀者會發(fā)現,(如果跑過我分享的仿真模型)在上一篇的文章圖中,ZCD latch S 的觸發(fā)信號,使用了一個比較投機取巧的方法。上下管驅動一定是需要死區(qū)時間的。將下管的 PWM 信號在 delay 一定的時間獲得 ZCDTrigger 信號,將兩者異或,就可以獲得一個從下管 PWM 開始的脈沖信號。

這樣做的好處是,下管 PWM 開始時刻,足夠保證 SW 電壓已經降低到負的二極管鉗位電壓。

再回頭來看 DCAP 框圖,ZCD latch Q 拉高,將 SW 接入 過零比較器 Zero-crossing Comparator 與 GND 比較。當 SW 電壓大于 GND 時,說明電感電流已經過零了,此時需要關斷下管的 PWM 信號。而下管的 PWM 信號與 ZCD latchQ 信號是相與關系,因此只要拉低 ZCD latch Q 即可,也即置位 ZCD latch R 端。

當電感電流過零時,過零比較器的輸出與 PWM latch Q 信號相或,此時 PWM latch Q 信號一定是低電平,則它倆的或門輸出為高電平,或門之后接了一個與門。與門的另一端是最小關斷定時器的比較器輸出與 PWM latch Q 相或后的信號,根據之前的分析,只有 Coff 電容充電階段,最小關斷定時器的比較器輸出與 PWM latch Q 相或后的信號才為低電平,其他時刻均為高電平。所以,與門的輸出信號,在 Coff 電容充電結束以及過零比較器輸出拉高時,一定為高電平,從而置位 ZCD latchR 端,順利地關閉下管的 PWM 信號。

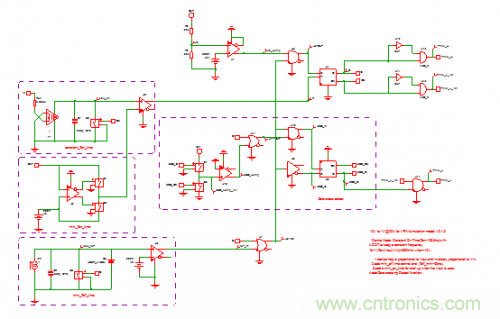

圖 44 simplisDCAP 仿真

在 Simplis 仿真方面,基本控制框圖類似,ZCD 檢測基本和 DCAP 控制框圖保持一致,增加了 PWM 驅動死區(qū)時間。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請電話或者郵箱聯系小編進行侵刪。