【導(dǎo)讀】最高 18 位分辨率、10 MSPS 采樣速率的逐次逼近型模數(shù)轉(zhuǎn)換 器(ADC)可以滿足許多數(shù)據(jù)采集應(yīng)用的需求,包括便攜式、工業(yè)、醫(yī)療和通信應(yīng)用。本文介紹如何初始化逐次逼近型 ADC 以實現(xiàn)有效轉(zhuǎn)換。

逐次逼近型架構(gòu)

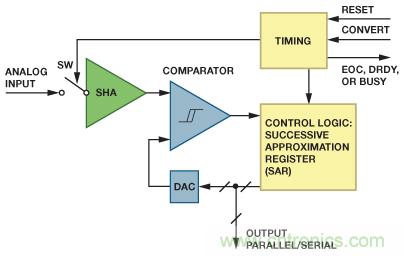

逐次逼近型ADC由4個主要子電路構(gòu)成:采樣保持放大器(SHA)、 模擬比較器、參考數(shù)模轉(zhuǎn)換器(DAC)和逐次逼近型寄存器(SAR)。 由于 SAR 控制著轉(zhuǎn)換器的運行,因此,逐次逼近型轉(zhuǎn)換器一般 稱為SAR ADC。

圖 1 基本 SAR ADC 架構(gòu)

在上電和初始化之后,CONVERT 上的一個信號會啟動轉(zhuǎn)換。 開關(guān)閉合,將模擬輸入連接至 SHA,后者獲得輸入電壓。當(dāng)開 關(guān)斷開時,比較器將確定模擬輸入(此時存儲于保持電容)是 大于還是小于 DAC 電壓。開始時,最高有效位(MSB)開啟, 將 DAC 輸出電壓設(shè)為中間電平。在比較器輸出建立之后,如 果 DAC 輸出大于模擬輸入,逐次逼近寄存器將關(guān)閉 MSB;如 果輸出小于模擬輸入,則會使其保持開啟。下一個最高有效位 會重復(fù)這一過程,如果比較器確定 DAC 輸出大于模擬輸入, 則關(guān)閉 MSB;如果輸出小于模擬輸入,則會使其保持開啟。 這個二進制搜索過程將持續(xù)下去,直到寄存器中的每一位都測 試完畢為止。結(jié)果得到的 DAC 輸入是采樣輸入電壓的數(shù)字近 似值,并由 ADC 在轉(zhuǎn)換結(jié)束時輸出。

與 SAR轉(zhuǎn)換代碼相關(guān)的因素

本文將討論與有效首次轉(zhuǎn)換相關(guān)的下列因素:

● 電源順序(AD765x-1)

● 訪問控制(AD7367)

● RESET (AD765x-1/AD7606)

● REFIN/REFOUT (AD765x-1)

● 模擬輸入建立時間(AD7606)

● 模擬輸入范圍(AD7960)

● 省電/待機模式(AD760x)

● 延遲(AD7682/AD7689、AD7766/AD7767)

● 數(shù)字接口時序

電源序列

些采用多個電源的ADC擁有明確的上電序列。AN-932應(yīng)用筆記電源序列, 列為這些ADC電源的設(shè)計提供了良好的參考。應(yīng)該特別 注意模擬和參考輸入,因為這些一般不得超過模擬電源電壓0.3 V 以上。 因此, AGND – 0.3 V < VIN < VDD + 0.3 V 且 AGND – 0.3 V < VREF < VDD + 0.3V。 模擬電源應(yīng)在模擬輸入或基準(zhǔn)電壓之前開啟, 否則,模擬內(nèi)核可能會以閂鎖狀態(tài)上電。類似地,數(shù)字輸入應(yīng)在 DGND − 0.3 V和VIO + 0.3 V之間。I/O電源必須在接口電路之前 (或與其同時)開啟,否則,這些引腳上的ESD二極管可能變成 正偏,而且數(shù)字內(nèi)核可能以未知狀態(tài)上電。

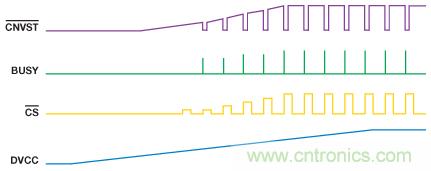

電源斜坡過程中的數(shù)據(jù)訪問

在電源穩(wěn)定之前不得訪問ADC,因為這樣可能使其進入未知狀 態(tài)。在圖 2 所示例子中,主機FPGA正在嘗試從 AD7367讀取數(shù) 據(jù),而DVCC正在斜升,結(jié)果可能使ADC進入未知狀態(tài)。

圖 2 在 DVCC 斜升過程中讀取數(shù)據(jù)

通過復(fù)位實現(xiàn) SAR ADC初始化

許多SAR ADC(如AD760x 和 AD765x-1在上電后需要通過 RESET來實現(xiàn)初始化。在所有電源都穩(wěn)定之后,應(yīng)施加一個指定 的RESET脈沖,以確保ADC以預(yù)期狀態(tài)啟動,同時使數(shù)字邏輯控 制處于默認狀態(tài),并清除轉(zhuǎn)換數(shù)據(jù)寄存器。上電時,電壓開始在REFIN/REFOUT 引腳上建立,ADC進入采集模式,同時配置用戶 指定模式。完全上電后,AD760x應(yīng)看到一個上升沿RESET將其 配置為正常工作模式。RESET高脈沖寬度典型值為50nss。

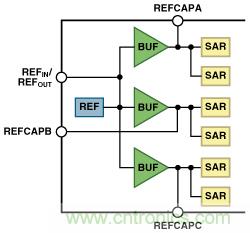

建立基準(zhǔn)電壓

ADC 將模擬輸入電壓轉(zhuǎn)換成指向基準(zhǔn)電壓的數(shù)字代碼,因此, 基準(zhǔn)電壓必須在首次轉(zhuǎn)換前穩(wěn)定下來。許多 SAR ADC 都有一 個 REFIN/REFOUT 引腳和一個 REF 或 REFCAP 引腳。外部基 準(zhǔn)電壓可能會通過 REFIN/REFOUT 引腳過驅(qū)內(nèi)部基準(zhǔn)電壓源, 或者,內(nèi)部基準(zhǔn)電壓源可能會直接驅(qū)動緩沖。REFCAP 引腳上的電容會使內(nèi)部緩沖輸出去耦,而這正是用于轉(zhuǎn)換的基準(zhǔn)電壓 源。圖 3 所示為 AD765x-1 數(shù)據(jù)手冊中的參考電路示例。

圖 3 AD765x-1 參考電路

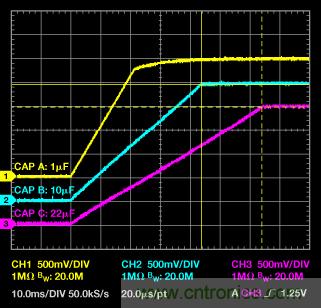

確保 REF 或 REFCAP 上的電壓在首次轉(zhuǎn)換之前已建立。壓擺 率和建立時間因不同的儲能電容而異,如圖 4 所示。

圖 4 AD7656-1 REFCAPA/B/C 引腳在不同電容下的電壓斜坡

另外,設(shè)計不佳的參考電路可能導(dǎo)致嚴重的轉(zhuǎn)換錯誤。參考電路 問題最常見的表現(xiàn)是"粘連"代碼,其原因可能是儲能電容的尺 寸和位置、驅(qū)動強度不足或者輸入存在大量噪聲。精密逐次逼近 型ADC的基準(zhǔn)電壓源設(shè)計 計作者:Alan Walsh (模擬對話第47卷第 2期,2013年)詳細討論了SAR ADC的基準(zhǔn)電壓源設(shè)計。

模擬輸入建立時間

對于多通道、多路復(fù)用應(yīng)用,驅(qū)動器放大器和 ADC 的模擬輸 入電路必須使內(nèi)部電容陣列以 16 位水平(0.00076%)建立滿量 程階躍。不幸的是,放大器數(shù)據(jù)手冊一般將建立精度指定為 0.1%或 0.01%。指定的建立時間可能與 16 位精度的建立時間 顯著不同,因此選擇驅(qū)動器之前應(yīng)進行驗證。

要特別注意多路復(fù)用應(yīng)用中的建立時間。在多路復(fù)用器切換 之后,要確保留出足夠的時間,以便模擬輸入能在轉(zhuǎn)換開始 之前建立至指定的精度。在配合AD7606使用多路復(fù)用器時, 應(yīng)為±10-V輸入范圍留出至少 80 µs的時間,為±5-V范圍留出 至少 88 µs,以便給選定通道足夠的時間來建立至 16 位分辨率面向精密SAR模數(shù)轉(zhuǎn)換器的前端放大器和RC濾波器設(shè)計作者:Alan Walsh(模擬對話 話第 46 卷第 4 期,2012 年)為放 大器的選擇提供了更多細節(jié)。

模擬輸入范圍

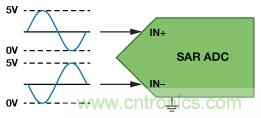

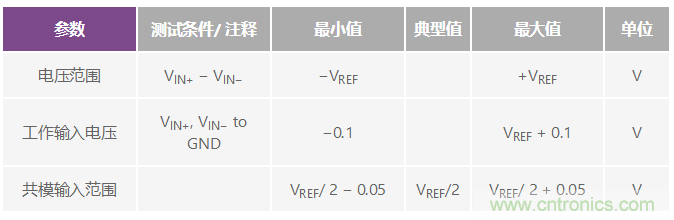

確保模擬輸入處于指定的輸入范圍之內(nèi),要特別注意指定共模 電壓的差分輸入范圍,如圖 5 所示。

圖 5 共模電壓下的全差分輸入

For example, the AD796018位、 5 MSPS SAR ADC的差分輸入范圍為–VREF 至 +VREF, 但折合到地的 VIN+ 和 VIN− −都應(yīng)該處于–0.1 V至 VREF + 0.1 V的范圍內(nèi),且共模電壓應(yīng)為 VREF/2左右,如表1所示。

表 1 AD7960的模擬輸入規(guī)格

使 SAR ADC退出關(guān)斷或待機模式

為了節(jié)能,有些SAR ADC會在空閑時進入關(guān)斷或待機模式。 在首次轉(zhuǎn)換開始前,要確保ADC退出該低功耗模式。例如, AD7606 系列即提供了兩種節(jié)能模式:完全關(guān)斷和待機。這些 模式由GPIO引腳STBY 和RANGE進行控制。

根據(jù)圖6所示,當(dāng)STBY 和RANGE返回高電平時,AD7606從完 全關(guān)斷進入正常工作模式,并配置為±10-V的范圍。此時, REGCAPA、REGCAPB和REGCAP引腳上電至數(shù)據(jù)手冊所述的 正確電壓。在進入待機模式時,上電時間約為 100 μs,但在外 部基準(zhǔn)電壓源模式下,這需要大約13 ms。從關(guān)斷模式上電時, 經(jīng)過所需的上電時間后,必須施加RESET信號。數(shù)據(jù)手冊將上 電與RESET上升沿之間所需時間規(guī)定為 tWAKE-UP SHUTDOWN。

圖 6 AD7606 初始化時序

帶延遲的 SAR ADC

人們普遍認為,SAR ADC 沒有延遲,但有些 SAR ADC 確實 存在延遲以便更新配置,因此,在經(jīng)過延遲時間(可能為數(shù)個 轉(zhuǎn)換周期)之前,第一個有效轉(zhuǎn)換代碼可能未定義。

例如,AD7985擁有兩種轉(zhuǎn)換工作模式:turbo和正常。Turbo模 式(支持最快的轉(zhuǎn)換速率,最高可達2.5 MSPS)不會在轉(zhuǎn)換間 關(guān)斷。turbo模式下的第一次轉(zhuǎn)換含有無意義的數(shù)據(jù),應(yīng)該予以 忽略。另一方面,在正常模式下,第一次轉(zhuǎn)換是有意義的。

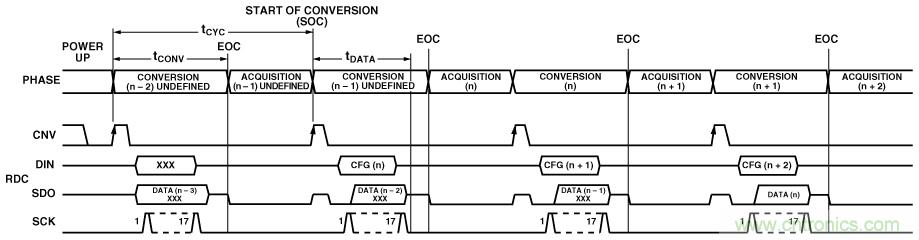

對于AD7682/AD7689, 上電后的前三個轉(zhuǎn)換結(jié)果未定義,因為 在第二個EOC之前,不會出現(xiàn)有效的配置。因此,需要兩次偽 轉(zhuǎn)換,如圖 7 所示。

圖 7 AD7682/AD7689 的通用時序

當(dāng)在硬件模式下使用 AD765x-1 時,在 BUSY 信號下降沿對 RANGE 引腳的邏輯狀態(tài)進行采樣,以決定下一次同步轉(zhuǎn)換的 模擬輸入范圍。在有效的 RESET 脈沖之后,AD765x-1 將默認 在±4 × VREF 范圍內(nèi)工作,無延遲問題。然而,如果 AD765x-1 工作于±2 × VREF 范圍內(nèi),則必須利用偽轉(zhuǎn)換周期在 BUSY的 第一個下降沿選擇范圍。

另外,有些SAR ADC(如AD7766/AD7767過采樣SAR ADC) 有后數(shù)字濾波器,結(jié)果會導(dǎo)致更多延遲。當(dāng)將模擬輸入多路復(fù) 用至這類ADC時,主機必須等到數(shù)字濾波器完全建立后才能獲 得有效轉(zhuǎn)換結(jié)果;經(jīng)過該建立時間后,方可切換通道。

如表 2 所示,AD7766/AD7767 的延遲為 74 除以輸出數(shù)據(jù)速率 (74/ODR)的商值。在運行于最高輸出數(shù)據(jù)速率 128 kHz 時, AD7766/AD7767 支持 1.729 kHz 的多路復(fù)用器開關(guān)速率。

表 2 AD7766/AD7767的數(shù)字濾波器延遲

數(shù)字接口時序

最后,但同樣重要的是,主機可以通過一些常見的接口選項(如 并行、并行 BYTE、IIC、SPI 和菊花鏈模式下的 SPI)來訪問 SAR ADC 的轉(zhuǎn)換結(jié)果。要得到有效的轉(zhuǎn)換數(shù)據(jù),必須確保遵 循數(shù)據(jù)手冊中的數(shù)字接口時序規(guī)格。

結(jié)論

為了獲得 SAR ADC 的第一個有效轉(zhuǎn)換代碼,務(wù)必遵循本文討 論的建議??赡苓€需要其他具體配置支持;請查看目標(biāo) SAR ADC 數(shù)據(jù)手冊或者應(yīng)用筆記,了解關(guān)于第一個轉(zhuǎn)換周期開始 之前初始化的相關(guān)內(nèi)容。

參考電路

Kester, Walt. Data Converter Support Circuits. Chapter 7, Data Conversion Handbook.

Kester, Walt. “Which ADC Architecture Is Right for Your Application?” Analog Dialogue, Volume 39, Number 2, 2005.

Walsh, Alan. “Front-End Amplifier and RC Filter Design for a Precision SAR Analog-to-Digital Converter.” Analog Dialogue, Volume 46, Number 4, 2012.

推薦閱讀: