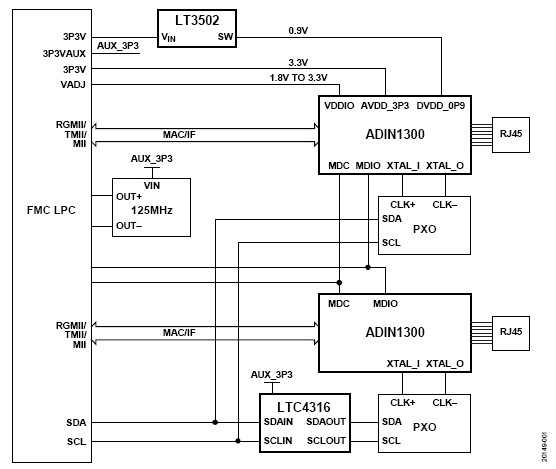

【導(dǎo)讀】圖1所示電路是一種雙通道、低延遲、低功耗的以太網(wǎng)物理層(PHY)卡,支持10 Mbps、100 Mbps和1000 Mbps速度,適合于采用線形和環(huán)形網(wǎng)絡(luò)拓撲的工業(yè)以太網(wǎng)應(yīng)用。

電路功能與優(yōu)勢

圖1所示電路是一種雙通道、低延遲、低功耗的以太網(wǎng)物理層(PHY)卡,支持10 Mbps、100 Mbps和1000 Mbps速度,適合于采用線形和環(huán)形網(wǎng)絡(luò)拓撲的工業(yè)以太網(wǎng)應(yīng)用。

雙通道支持常用于工業(yè)檢測、控制和分布式控制系統(tǒng)的線形和環(huán)形網(wǎng)絡(luò)拓撲。ADIN1300以太網(wǎng)PHY針對電磁兼容性(EMC)和靜電放電(ESD)魯棒性進行了廣泛的測試,并支持自動協(xié)商,能夠以宣傳的最高通用速度與遠程PHY器件鏈接。PHY中的IEEE 1588時間戳降低了實時應(yīng)用中的時序不確定性,并增強了冗余和實時應(yīng)用的鏈路損耗檢測。

該電路由兩個獨立的10 Mbps、100 Mbps和1000 Mbps PHY組成,每個PHY均有一個高能效以太網(wǎng)(EEE) PHY內(nèi)核及所有相關(guān)的通用模擬電路、輸入輸出時鐘緩沖、管理接口、子系統(tǒng)寄存器、媒介訪問控制(MAC)接口和控制邏輯。

該設(shè)計由主機現(xiàn)場可編程門陣列(FPGA)夾層卡(FMC)開發(fā)板供電,無需外部電源。軟件可編程時鐘支持媒介獨立接口(MII)、精簡MII (RMII)和精簡千兆位MII (RGMII) MAC接口模式。集成磁性元件的RJ45端口使解決方案盡可能緊湊。

該解決方案在千兆速度下支持最長150米電纜,在100 Mbps或10 Mbps速率下支持最長180米電纜。該解決方案通常用于環(huán)形或總線拓撲。ADIN1300的自動協(xié)商特性允許以支持的最高速度與其他PHY器件連接。

圖1.EVAL-CN0506-FMCZ簡化框圖(未顯示解耦和所有連接)

電路描述

以太網(wǎng)

以太網(wǎng)是局域網(wǎng)(LAN)中數(shù)據(jù)網(wǎng)絡(luò)應(yīng)用最常見的基于分組的物理連接類型,由電氣電子工程師協(xié)會(IEEE) 802.3標準的多個小節(jié)和規(guī)范定義。

以太網(wǎng)具有不同的速度和傳輸媒介。但是,本電路筆記的重點是直通或交叉、5e類(CAT5e)或6類(CAT6)雙絞線電纜上的10BASE-T、100BASE-TX和1000BASE-T。

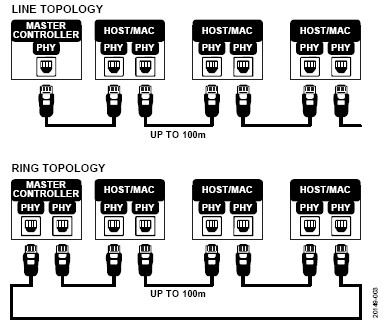

線形和環(huán)形網(wǎng)絡(luò)拓撲

典型工業(yè)以太網(wǎng)網(wǎng)絡(luò)采用線形或環(huán)形拓撲進行部署。與星形網(wǎng)絡(luò)相比,線形和環(huán)形網(wǎng)絡(luò)拓撲的布線長度更短,而且環(huán)形網(wǎng)絡(luò)還有一條冗余路徑(參見圖2)。連接至線性或環(huán)形網(wǎng)絡(luò)的每個設(shè)備都需要兩個以太網(wǎng)端口,以便沿網(wǎng)絡(luò)傳遞以太網(wǎng)幀。

圖2.線形和環(huán)形拓撲

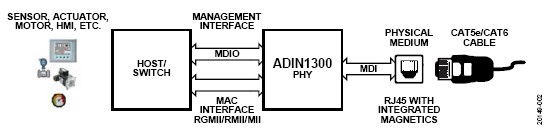

PHY

PHY是實現(xiàn)開放系統(tǒng)互連(OSI)模型的物理層功能的物理接口收發(fā)器。PHY對器件之間發(fā)送和接收的數(shù)據(jù)進行編碼和解碼,從而保持幀和數(shù)據(jù)包的完整性(參見圖3)。

PHY硬件配置—綁定電阻

可以將ADIN1300配置為上電就緒以建立鏈路。此PHY硬件配置使用外部綁定電阻,為非托管應(yīng)用中的上電操作提供一個已知配置。在非托管應(yīng)用中,用戶通常不會在管理數(shù)據(jù)輸入輸出(MDIO)上配置PHY。相反,非托管應(yīng)用依賴PHY硬件配置以適當?shù)呐渲脝覣DIN1300,從而準備好與遠程PHY伙伴鏈接。當ADIN1300上電時,硬件綁定引腳在器件退出復(fù)位狀態(tài)時進行采樣,這樣PHY器件便知道如何配置各種功能。

本電路筆記關(guān)注的硬件配置模式是速度、PHY地址、自動媒介相關(guān)接口交叉(Auto-MDIX)和MAC接口。EVAL-CN0506-FMCZ包含多種尺寸的電阻以支持各種組合,并有一個特定的默認配置。如果需要更改默認硬件配置,可以插入或卸下電阻元件。

有關(guān)使用其他特性和功能(例如高能效以太網(wǎng)(EEE)、能量檢測關(guān)斷、關(guān)斷速度和軟件關(guān)斷)的更多信息,請查閱ADIN1300數(shù)據(jù)手冊。

圖3.帶有PHY器件的典型網(wǎng)絡(luò)傳感器

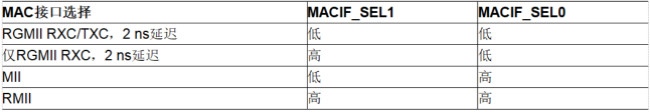

物理層—MAC接口

MAC接口是CN-0506上的有線媒介,有三個MAC接口選項:RGMII、RMII或MII。RGMII支持所有速度,最高為1000 Mbps,而MII和RMII分別支持10 Mbps和100 Mbps。RGMII是CN0506的默認接口。

選擇使用哪種MAC接口有兩種方法:通過硬件綁定外部電阻,或使用軟件寄存器配置。MACIF_SEL0和MACIF_SEL1是ADIN1300內(nèi)的多功能引腳(更多信息參見ADIN1300數(shù)據(jù)手冊)。對于CN-0506,可以根據(jù)表1配置MACIF_SEL0和MACIF_SEL1引腳以選擇MAC接口。請注意,MACIF_SEL0和MACIF_SEL1引腳內(nèi)部有弱下拉電阻。因此,如果沒有外部綁定電阻,則默認MAC接口為2 ns延遲的RGMII。

表1.MAC接口選擇

在本電路筆記中,MAC接口選擇通過軟件配置完成,即使用ADIN1300中的GE_RGMII_CFG和GE_RMII_CFG寄存器。如果用戶更愿意在硬件中配置MAC接口,板上也為外部上拉和下拉電阻預(yù)留了空間。但是,由于未安裝電阻,故EVAL-CN0506-FMCZ上的PHY使用默認RGMII接口上電。

PHY地址

有四個PHY地址引腳(PHYAD_x),允許用戶將PHY配置為16個PHY地址中的任何一個。PHY尋址使得系統(tǒng)可以從單個控制器獲得多達16個獨立可控通道。

EVAL-CN0506-FMCZ當前已硬連線為特定地址,但可以通過更改每個通道的配置電阻來改變。通道1當前分配的地址為0001,通道2當前分配的地址為0010。

可編程MAC接口時鐘

ADIN1300具有三個MAC接口選項:MII、RMII或RGMII。對于RGMII和MII接口,ADIN1300需要25 MHz的時鐘,而RMII需要外部50 MHz的時鐘。在用戶應(yīng)用中,用戶可以選擇將25 MHz晶振放在XTAL_I和XTAL_O引腳附近,或者對于使用RMII的情況,主機控制器、MAC接口或交換芯片可以直接向PHY提供所需的50 MHz時鐘。

EVAL-CN0506-FMCZ包括兩個從100 kHz到125 MHz的I2C可編程時鐘(Y1和Y2),以支持ADIN1300不同MAC接口的相應(yīng)時鐘需求。

默認情況下,上電時每個通道的時鐘設(shè)置為25 MHz。使用RMII MAC接口時,可以將時鐘編程為50 MHz。

兩個時鐘具有相同的I2C地址,但通過使用I2C地址轉(zhuǎn)換器LTC4316,這些時鐘可以分別編程為彼此不同的地址。LTC4316對傳入的地址進行XOR運算,將每個傳入的位轉(zhuǎn)換為由芯片的電阻分壓器網(wǎng)絡(luò)設(shè)置的用戶可配置轉(zhuǎn)換字節(jié)。

MDI接口—集成磁性元件

通常,MDI接口通過變壓器和RJ45連接器將ADIN1300連接到以太網(wǎng)。CN-0506使用集成磁性元件的RJ45連接器。RJ45連接器中集成的磁性元件通??梢愿纳齐姶鸥蓴_(EMI)屏蔽,并且尺寸較小,與使用分立磁性元件相比,所需的走線布線更短。

集成磁性元件包括RJ45連接器、共模扼流圈、隔離變壓器、LED、解耦電容和端接電阻。由于設(shè)計中的過壓要求不同,或者如果特定EMI需要不同布局,設(shè)計可以選擇使用分立磁性元件。

電源

為了減少電源數(shù)量,ADIN1300、MDIO和MAC接口的模擬電路電源通過鐵氧體磁珠從FPGA的3.3 V供電軌獲取,以減少進入系統(tǒng)的噪聲。

ADIN1300的數(shù)字內(nèi)核需要0.9 V電源。該電源是在板上利用LT3502脈沖寬度調(diào)制(PWM)降壓DC-DC轉(zhuǎn)換器從3.3 V供電軌獲??;轉(zhuǎn)換器將FPGA的3.3 V電源轉(zhuǎn)換為0.9 V,消耗的載波功率最大為0.45W。

軟件概述

提供給CN-0506使用的FPGA參考設(shè)計獨立配置每個ADIN1300。每個PHY (ADIN1300)連接到指定的MAC接口,ADIN1300和FPGA之間支持三種接口模式:RGMII、MII和RMII。

每種模式都有單獨的硬件設(shè)計語言(HDL),因為某些模式需要轉(zhuǎn)換器,例如千兆MII (GMII)轉(zhuǎn)RGMII。工作模式須在HDL中選擇,以與用戶希望在Linux中使用的模式一致。

EVAL-CN0506-FMCZ連接到標準低引腳數(shù)(LPC) FMC連接器,軟件設(shè)計可移植到許多不同的FPGA開發(fā)板上。

不同模式和載波組合支持的Linux設(shè)備樹可以在CN0506 HDL頁面上找到。有關(guān)ADI公司標準Linux鏡像的更多信息,參見FPGA鏡像用戶指南。

電路板布局考量

以太網(wǎng)信號布局至關(guān)重要,尤其是在千兆速度下。信號以100Ω受控阻抗對的形式路由到RJ45插孔。

以較低時鐘速率運行時,到載波的數(shù)據(jù)和時鐘信號具有邊沿速率,要求小心布局。EVAL-CN0506-FMCZ上的信號應(yīng)保持盡可能短,連接CN-0506時必須仔細考慮載板上的信號走線長度和阻抗匹配。這些因素對CN-0506的整體速度和性能很重要,但必須分別考慮。

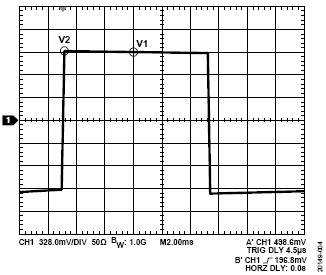

圖4顯示了從V2到V1的1000BASE-T最大下降點——98.7%。

圖4.峰值PHY差分輸出電壓

性能結(jié)果

使用CN-0506進行了一些測試,包括模式驗證測試、速度測試和電纜長度驅(qū)動測試。

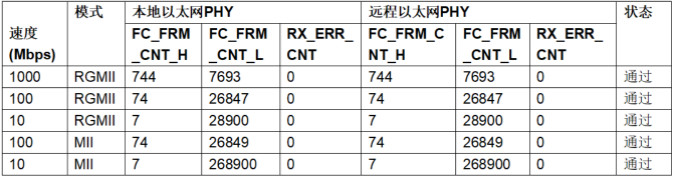

EVAL-CN0506-FMCZ在不同模式下進行了測試,電纜長度逐漸增加。4米電纜和154米電纜的結(jié)果已在表2和表3中分別詳細列出,沒有丟包。

表2和表3分別顯示了短電纜傳輸和長電纜傳輸情況下本地和遠程以太網(wǎng)PHY位置上ADIN1300的幀檢查器計數(shù)寄存器(FC_FRM_CNT_H和FC_FRM_CNT_L)和接收錯誤計數(shù)寄存器(RX_ERR_CNT)的回讀值。

表2.使用4米電纜的EVAL-CN0506-FMCZ評估系統(tǒng)

表3.使用154米電纜的EVAL-CN0506-FMCZ評估系統(tǒng)

常見變化

如果應(yīng)用不需要高達1000 Mbps的速度,可使用功耗更低的單端口以太網(wǎng)收發(fā)器ADIN1200,其最高速度為100 Mbps。

關(guān)于I2C總線轉(zhuǎn)換器的替代產(chǎn)品,LTC4317是一款單輸入、雙輸出I2C地址轉(zhuǎn)換器,而LTC4318是一款雙輸入輸出I2C總線轉(zhuǎn)換器。

如果應(yīng)用不需要RMII支持,則僅使用一個固定頻率的25 MHz晶振可簡化時鐘方案。

電路評估與測試

數(shù)據(jù)完整性和帶寬在工業(yè)網(wǎng)絡(luò)中至關(guān)重要。數(shù)據(jù)回送測試可以驗證整個系統(tǒng),包括EVAL-CN0506-FMCZ、電纜和連接器。有關(guān)設(shè)置和測試的完整詳細信息,參見CN0506用戶指南。

設(shè)備要求

需要以下設(shè)備:

•EVAL-CN0506-FMCZ電路評估板

•CAT6以太網(wǎng)電纜

•ZC706 FPGA開發(fā)板

•SD卡

•帶有USB A型加密狗的無線鍵盤和鼠標

•微型USB OTG適配器

•高清多媒體接口(HDMI)公對公電纜

•HDMI監(jiān)視器

•ADI公司Linux鏡像,配置為與CN0506一起使用

開始使用

按照適用于Zynq和Altera SoC的AD-FMC-SDCARD快速入門指南中的詳細說明準備SD卡,包括以下內(nèi)容:

1. 下載最新的FPGA Linux鏡像。

2. 格式化SD卡。

3. 將FPGA Linux鏡像燒錄到SD卡。

4. 將CN-0506的boot.bin和設(shè)備樹文件復(fù)制到SD卡的引導(dǎo)分區(qū)中。

功能框圖

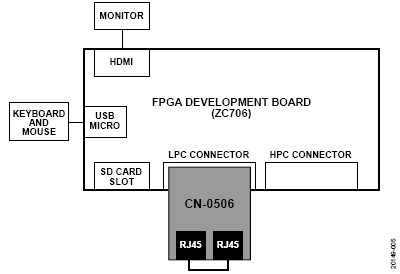

圖5所示為測試設(shè)置的功能框圖。

圖5.測試設(shè)置功能框圖

設(shè)置

請執(zhí)行以下步驟來設(shè)置測試:

1. 使用LPC FMC連接器將EVAL-CN0506-FMCZ安裝到ZC706 FPGA開發(fā)板上,并用10mm支柱將其固定。

2. 將預(yù)先配置的SD卡插入Xilinx ZC706。

3. 在兩個RJ45以太網(wǎng)插孔之間連接以太網(wǎng)電纜,以建立回送。

4. 在HDMI監(jiān)視器和Xilinx ZC706之間連接HDMI電纜。

5. 將微型USB OTG適配器插入Xilinx ZC706的微型USB端口。

6. 使用USB A型加密狗將無線鍵盤和鼠標連接到USB OTG適配器。

7. 將電源連接器連接至Xilinx ZC706,并將另一端插入壁式電源適配器。

測試

在回送模式下測試系統(tǒng),即生成大量數(shù)據(jù),并將數(shù)據(jù)從一個通道發(fā)送到另一個通道,然后送回來。

圖6顯示了EVAL-CN0506-FMCZ電路評估板的實物照片。

圖6.EVAL-CN0506-FMCZ電路評估板

有關(guān)測試設(shè)置以及如何使用EVAL-CN0506-FMCZ的完整信息和細節(jié),請參閱CN0506用戶指南。

推薦閱讀: