【導(dǎo)讀】隨著芯片制造成本的不斷上升和復(fù)雜性的不斷增加,使得今年成為了半導(dǎo)體產(chǎn)業(yè)合并和尋找替代性技術(shù)創(chuàng)記錄的一年。工程師們在IEEE S3S會議上肯定聽說了許多的合并傳聞,包括絕緣硅、亞閾值電壓設(shè)計、單片3D集成以及行業(yè)重組等。

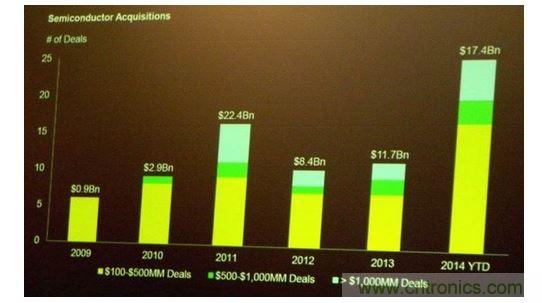

今年到目前為止芯片公司已經(jīng)完成了23筆收購交易,這要比過去兩年的總和還多,摩根士丹利公司半導(dǎo)體投資銀行全球負(fù)責(zé)人Mark Edelstone透露。他同時預(yù)測今年的全球并購交易總值很可能從174億美元增加到近300億美元。

"情況真的是破記錄了。"他指出,并提到了至今較大的整合案例--英飛凌和國際整流器公司以及安華高和LSI公司。"這個趨勢將繼續(xù),今后幾年將是非常繁忙的并購時期。"

圖1:2014年發(fā)生的半導(dǎo)體并購交易量已經(jīng)超過過去兩年的總和。

較低的資本成本正在所有行業(yè)掀起并購浪潮,而制造芯片成本和復(fù)雜性的上升助推了半導(dǎo)體行業(yè)的并購。制造一個20nm芯片的成本需要5300萬美元,制造28nm芯片的成本是3600萬美元,到16/14nm節(jié)點時成本還將出現(xiàn)質(zhì)的飛躍,Edelstone表示。

"在這樣的投資規(guī)模下要想賺錢需要非常大的市場,這對半導(dǎo)體行業(yè)的發(fā)展將帶來巨大的影響。到16/14 nm的FinFET時代,每個門的成本還將上升,這將顯著地改變半導(dǎo)體行業(yè)現(xiàn)狀--事實表明,規(guī)模決定成敗。"

多位發(fā)言人一致認(rèn)為單個晶體管的成本在整個行業(yè)中還在不斷上升。不過Intel公司在今年9月份透露,其14nm FinFET工藝將支持更低的每晶體管成本。

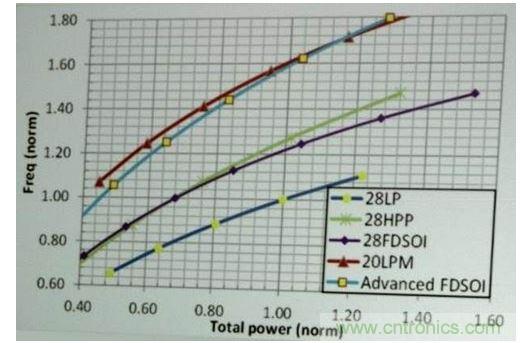

14/16nm FinFET節(jié)點代表了今后發(fā)展的主流方向,但完全耗盡型和特薄絕緣硅工藝也有機會,GlobalFoundries公司產(chǎn)品經(jīng)理Michael Medicino表示。

一些對成本敏感的移動芯片因為成本原因會避免采用14nm和10nm FinFET節(jié)點,而且時間可能長達(dá)4至6年。絕緣硅(SOI)提供了另外一種替代方案,它可以達(dá)到20nm塊晶體管的性能,成本則接近28nm聚合物晶體管,不過他認(rèn)為在市場壓力下所有塊晶體管成本還會進一步下降。

Mendicino預(yù)計絕緣硅替代技術(shù)在今后三年中可能占據(jù)10%的代工業(yè)務(wù)份額,不過他強調(diào)這只是猜測。"三年后再問我吧。"他不無俏皮地說。

[page]

在一次單獨的交談中,聯(lián)發(fā)科公司高性能處理器技術(shù)總監(jiān)Alice Wang介紹了亞閾值設(shè)計的例子。他們的雄心壯志是推動芯片達(dá)到漏電流和動態(tài)能量交匯的最小能量點,這是在她的博士論文和ISSCC 2004論文中提出的一個概念。

工程師們已經(jīng)向這個艱巨的目標(biāo)努力了近一年。他們接下來面臨的挑戰(zhàn)是提供仍然能夠完成有意義的工作、可靠并且具有最小開銷的芯片,Alice指出。

大規(guī)模并行架構(gòu)可以幫助提供超低功耗芯片在媒體處理任務(wù)中有所作為所需的性能。時序收斂方面的新方法與新工具可以解決一些可靠性和開銷問題,她表示。

"我認(rèn)為現(xiàn)在是超低電壓(ULV)成為我們?nèi)粘I钜徊糠值臅r候了。"她在提到發(fā)展中市場出現(xiàn)的可佩戴和設(shè)計問題時指出。"世界上還有大約13億人還沒有電力供應(yīng)……因此能量是新興市場面臨的真正關(guān)鍵的挑戰(zhàn)。"

圖2:下一代絕緣硅能以28nm聚合物晶體管的價格提供20nm的性能。

此次大會的組織者Zvi Or-Bach特別提到了會議期間舉辦的兩次小組討論會,會中討論了如何擴展目前正在最新閃存芯片中采用的單片3D設(shè)計種類。

在其中一個討論會中,來自CEA-Leti公司和意法半導(dǎo)體公司的研究人員介紹了單片3D集成技術(shù),這是應(yīng)對2D芯片縮放不斷上升的成本而開發(fā)的一種替代性技術(shù)。他們在一個FPGA案例研究中發(fā)現(xiàn),這種技術(shù)與傳統(tǒng)堆棧結(jié)構(gòu)相比可以減小55%的面積。研究報告中寫道:

單片3D集成技術(shù)旨在按上下順序一個接一個地處理晶體管。然而,它的實現(xiàn)面臨著許多挑戰(zhàn),比如能夠在溫度低于600℃的情況下實現(xiàn)高性能的頂部晶體管、以便在頂部堆棧式FET制造過程中防止底部FET出現(xiàn)性能劣化……固定相位外延再生長已證明其效率包含600℃左右的熱預(yù)算,而且向下變化時也有望具有高效率。

另外,EV Group和尼康公司代表分享了用于綁定和對準(zhǔn)系統(tǒng)的新功能細(xì)節(jié),它們能夠避免當(dāng)前3D芯片堆棧中使用的硅通孔的高成本和高復(fù)雜性。

EV Group公司介紹了綁定對準(zhǔn)精度為200nm或以下的一個演示例子。Nikon介紹了一種新的EGA精密晶圓綁定技術(shù),"它可以獲得好于250nm的穩(wěn)定度和更高對準(zhǔn)精度……可以用來制造未來的3D IC,如DRAM、MPU和圖像傳感器。"