【導讀】通過多路復用,每個系統(tǒng)可以使用更少的ADC,從而顯著節(jié)省功耗、尺寸和成本。本文重點討論采用高性能精密SAR型ADC的多路復用數(shù)據(jù)采集系統(tǒng)的重要設(shè)計考慮、性能效果和應(yīng)用挑戰(zhàn)。

通過多路復用,每個系統(tǒng)可以使用更少的ADC,從而顯著節(jié)省功耗、尺寸和成本。逐次逼近型ADC(因為其采用逐次逼近型寄存器而常常稱為SAR型ADC)具有低延遲特性,很受多路復用系統(tǒng)的歡迎——這些系統(tǒng)要求對滿量程輸入步進(最差情況)做出快速響應(yīng),而不會產(chǎn)生任何建立時間方面的問題。 SAR型ADC易于使用,功耗很低,并且尺寸較小。

本文重點討論采用高性能精密SAR型ADC的多路復用數(shù)據(jù)采集系統(tǒng)的重要設(shè)計考慮、性能效果和應(yīng)用挑戰(zhàn)。

切換多路復用器的輸入通道時,ADC驅(qū)動放大器必須在規(guī)定的采樣周期內(nèi)完成大電壓步進的建立。 輸入可能會從負滿量程變換到正滿量程或從正滿量程變換到負滿量程,因此可能在很短的時間內(nèi)產(chǎn)生大輸入電壓步進。 為了處理這種步進,放大器必須具有寬信號帶寬和快速建立時間。此外,壓擺率或輸出電流限制會引起非線性效應(yīng)。

另外,驅(qū)動放大器還必須解決采集周期開始時SAR型ADC輸入端的電荷再平衡所導致的反沖影響。這可能會成為多路復用系統(tǒng)輸入建立的瓶頸。通過降低ADC的吞吐速率,從而延長采集時間并使放大器有足夠的時間建立至要求的精度,可以緩解建立時間問題。

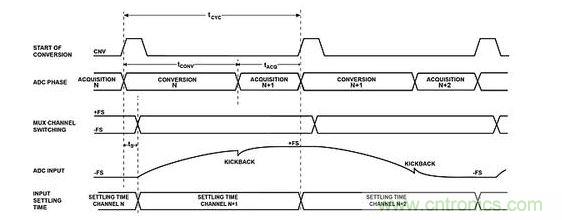

圖1中的時序圖顯示了輸入幅度發(fā)生滿量程變化時,如何優(yōu)化每通道建立時間。ADC的周期時間通常包括轉(zhuǎn)換時間和采集時間(tCYC = tCONV + tACQ),在數(shù)據(jù)手冊中一般規(guī)定為吞吐速率的倒數(shù)。 轉(zhuǎn)換開始時,SAR型ADC的容性DAC與輸入端斷開,經(jīng)過很短的開關(guān)延遲tS后,便可將多路復用器通道切換至下一通道。這將為所選通道提供最長的建立時間。

為了保證最大吞吐速率時的性能,多路復用系統(tǒng)的所有器件都必須在多路復用器切換與采集時間結(jié)束之間的時間里在ADC輸入端完成建立。多路復用器通道切換必須與ADC轉(zhuǎn)換時間正確同步。多路復用系統(tǒng)可達到的吞吐速率等于單個ADC的吞吐速率除以采樣的通道數(shù)。

圖1 多路復用數(shù)據(jù)采集系統(tǒng)的典型時序圖

有些設(shè)計人員利用低輸出阻抗緩沖器處理多路復用器輸入端的反沖影響。SAR型ADC的輸入帶寬(數(shù)十MHz)和ADC驅(qū)動器的輸入帶寬(數(shù)百MHz)高于采樣頻率,期望的輸入信號帶寬通常在數(shù)十至數(shù)百kHz范圍內(nèi),因此,多路復用器的輸入端可能需要一個RC抗混疊濾波器,用以防止干擾信號(混疊)折回到目標帶寬并緩解建立時間問題。 各輸入通道使用的濾波器電容值應(yīng)根據(jù)以下考慮精心選擇:若容值較大,它將有助于衰減多路復用器的反沖,但它也會降低前一放大器級的相位裕量,使其變得不穩(wěn)定。

為使RC濾波器具有高Q、低溫度系數(shù),并且在變化電壓下具有穩(wěn)定的電氣特性,建議使用C0G或NP0型電容。應(yīng)選擇合理的串聯(lián)電阻值,使放大器保持穩(wěn)定并限制其輸出電流。 R不能過大,否則在多路復用器反沖后,放大器將不能給電容充電。